PCI-Express-Technologie wird seit langem verwendet, um Grafikkarten und andere Peripheriegeräte wie NVMe-SSDs anzuschließen. Die Implementierung der fünften Generation der Schnittstelle erfolgt mit der Ankunft der Alder-Lake-Prozessoren von Intel und die Zen 4-Prozessoren von AMD. Aber die PCI Express 6.0-Spezifikation wurde fertiggestellt und bringt mehrere Verbesserungen gegenüber der fünften Generation.

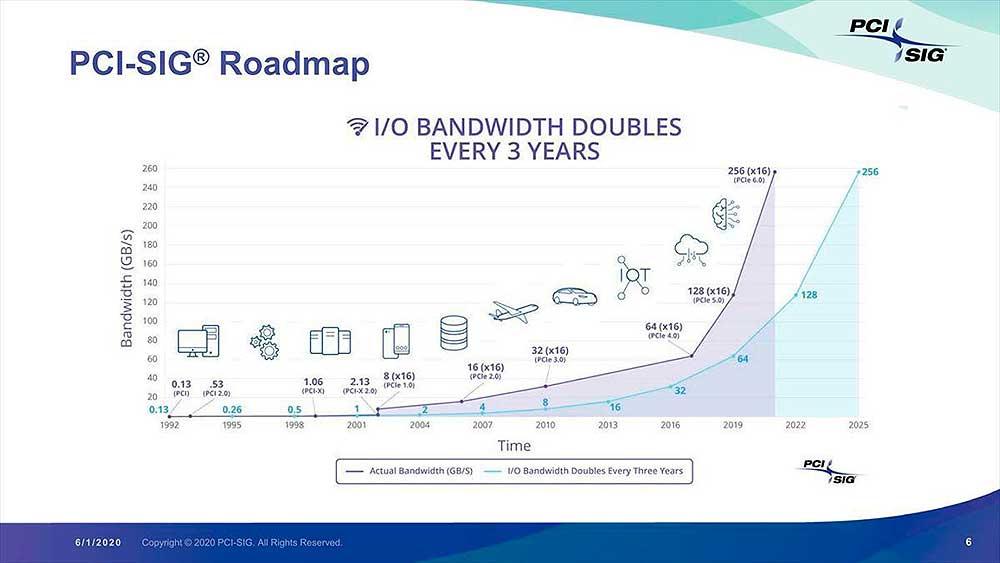

Der PCI Express 6.0 folgt von vornherein den gleichen Verbesserungen wie die Vorgängergenerationen dieser Schnittstelle, das heißt es basiert auf einer Verdoppelung der Bandbreite gegenüber der Vorgängergeneration. Im Fall von PCI Express 6.0 waren jedoch tiefgreifende Änderungen bei der Entwicklung der sechsten Generation dieser Schnittstelle erforderlich.

Die Bandbreite von PCI Express 6.0 beträgt 128 GB/s für eine 16-Line-Schnittstelle, eine übertrieben hohe Bandbreite für eine I/O-Schnittstelle und das ist ein vierfacher Sprung gegenüber dem aktuellen PCI Express 4.0, den wir für aktuelle Grafiken verwenden Karten. Der Sprung bedeutet auch einen Sprung von NVMe SSD Flash-Controller von 7-8 GB/s bis 28-32 GB/s mit PCI Express 6.0.

Abwärtskompatibilität und das Problem der Signalinstabilität

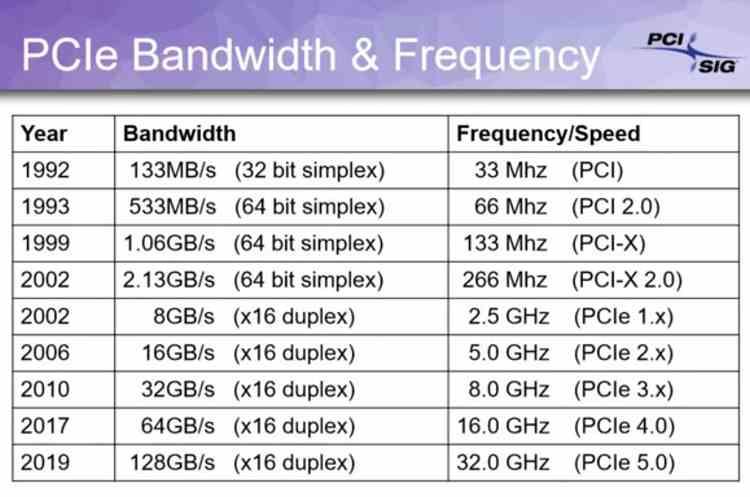

Die PCI Express-Schnittstelle war schon immer abwärtskompatibel mit früheren Versionen des Protokolls, das bedeutet, dass wir eine PCI Express 1.0-Karte in einen PCI Express 6.0-Steckplatz stecken können und es funktioniert, weil die Pinage genau gleich ist. Es ist also nicht möglich, die Anzahl der Pins zu erhöhen, um die Bandbreite zu erhöhen, ohne die Geschwindigkeit zu erhöhen. Die Lösung? Erhöhen Sie die Taktfrequenz, mit der die Schnittstelle arbeitet.

Das Problem mit PCI Express 6.0? Wenn wir die Taktrate einer Schnittstelle erhöhen, wird sie mit zunehmender Entfernung instabiler und nach sechs Generationen mussten sie aufgrund der hohen Geschwindigkeit, mit der die Schnittstelle traditionell arbeitet, Änderungen an der Schnittstelle vornehmen. Und wenn man sich die Tabelle ansieht, die diesen Zeilen beiliegt, sprechen wir von einer theoretischen Geschwindigkeit von 64 GHz, die das Signal ausreichend verformt, selbst bei der kurzen Entfernung befinden sich beide Enden in einer PCI-Express-Schnittstelle.

Dies hat eine Reihe von Maßnahmen erzwungen, um den Sprung auf PCI Express 6.0 zu ermöglichen.

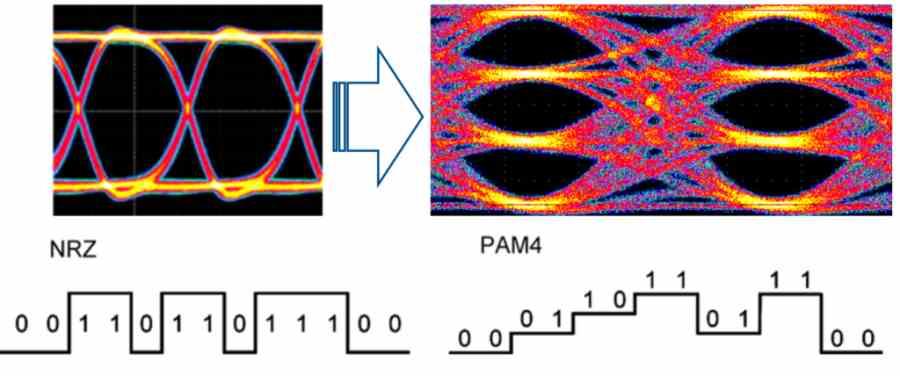

Erste der Verbesserungen in PCI Express 6.0, Verwendung von PAM4

Woher weiß eine externe oder interne Schnittstelle eines Chips, ob der Wert eine 1 oder eine 0 ist? Nun, ganz einfach, je nach Spannung, in der die Informationen übertragen werden. Binäre Systeme basieren auf der Verwendung von zwei Spannungen mit genügend Abstand zwischen ihnen, damit der Spannungsabfall oder -anstieg das Signal nicht verwechselt. Bei analogen Systemen setzt eine einfache Spannungsänderung eine Änderung der Information voraus. Aus diesem Grund sprechen Computer binär.

Was hat das mit PCI Express 6.0 zu tun? Da wir die Bandbreite nicht erhöhen können, weil das Signal verzerrt ist und auch nicht die Anzahl der Pins für die Abwärtskompatibilität, muss eine Lösung gefunden werden und dies geht über die Verwendung von PAM4-Kodierung oder Pulsamplitudenmodulation, die wir bereits beim GDDR6X gesehen haben und basiert nicht auf der Verwendung von zwei Spannungswerten, sondern 4 Spannungswerten für jeden Pin. Auf diese Weise können wir an jedem Pin die Werte 00, 01, 10 und 11 codieren. Insgesamt vier Werte anstelle der beiden klassischen Werte, die 0 oder 1 wären.

Die Lösung vermeidet eine Erhöhung der Bandbreite und der Pins, sagt uns aber, dass dies in PCI Express 7.0 mit herkömmlichen Methoden nicht mehr möglich sein wird. Wir sehen vielleicht den Einsatz von Photonik und optischen Schnittstellen, aber mit den Verbesserungen an PCI Express 6.0 frisch aus dem Ofen, sollten Sie mit dem Nachfolger besser geduldig sein.

Änderungen im Paketsystem

Der Sprung zu PAM-4 hat die Art und Weise verändert, in der die PCI Express 6.0-Schnittstelle ihre Pakete sendet, obwohl sie mit früheren Generationen kompatibel ist, indem sie im traditionellen PAM-2- oder NRZ-Modus kommuniziert. Die Realität ist, dass das PAM-4-Format das vorherige Paketsystem nicht unterstützt und sich daher das Kommunikationsprotokoll geändert hat.

Die erste Änderung war die sogenannte Forward Error Correction oder FEC, das neue Protokoll zur Korrektur von Fehlern beim Senden von Daten. Das Problem ist, dass die zu verarbeitende Bandbreite so hoch ist, dass die FEC beim Senden der Daten eine enorme Latenzzeit hinzufügt. Um dies zu mildern, verwendet der PCI Express 6.0-Standard einen Pakettyp namens FLIT. Ein Paket ist nichts anderes als eine Reihe von Bits mit einem bestimmten Ziel. Die Sendelatenz jedes FLIT? Dies hängt von der Anzahl der Leitungen auf der Schnittstelle ab, aber jedes Paket hat eine Latenzzeit von nur 2 ns auf einem 16-Leitungs-PCI Express 6.0, aber bis zu 32 ns auf einer Einzelleitungs-Schnittstelle.

Der FEC arbeitet nur mit festen Größen, deshalb hat der FLIT eine Größe von 256 Byte pro Send. Jedes Paket oder TLP kann eine Größe von 0 Byte bis 4096 Byte haben und daher kann jedes Paket aus mehreren FLITS bestehen.

Drittes Upgrade auf PCI Express 6.0, variabler Verbrauch

PCI Express 6.0 fügt einen neuen Low-Power-Status namens L0P hinzu. Dieser Modus ermöglicht es der Schnittstelle, ihren Stromverbrauch zu senken, wenn der gesendete Datenfluss geringer ist, als die Schnittstelle übertragen kann. Dazu variiert die Taktgeschwindigkeit, mit der die Schnittstelle zu bestimmten Zeitpunkten der Datenübertragung arbeitet, ohne dass es zu einer Unterbrechung kommt, die der Datenübertragung Latenzzeit hinzufügt.

Das Problem ist, dass dieser Mechanismus mit FLITS und FEC und damit mit PAM4 verbunden ist, was bedeutet, dass die Verwendung nur im PCI Express 6.0-Modus und nicht in den anderen Modi möglich ist.