แน่นอนว่าพวกคุณส่วนใหญ่ไม่ได้ตระหนักถึงความจริงที่ว่าเรากำลังอยู่บนทางแยก ซีพียู และ GPU มีความกังวล มาร์จิ้นมีไม่มาก มีเวลาไม่มาก และของที่เหลืออยู่กำลังจะหมดลง จำเป็นต้องมีการเปลี่ยนแปลงในส่วนประกอบที่เป็นพื้นฐานเช่นเดียวกับแนวคิดของการคำนวณ: ในทรานซิสเตอร์ อินเทล มีวิสัยทัศน์ของปัญหาและแนวทางแก้ไข: นี่จะเป็น Intel RibbonFET.

เพื่อทำความเข้าใจวิธีแก้ปัญหา ก่อนอื่นเราต้องตระหนักถึงปัญหา ทำความเข้าใจกับมัน และรู้ว่าขีดจำกัดคืออะไรที่จะทำเครื่องหมายเรา ในกรณีนี้ เราจะเริ่มต้นที่นั่นด้วยปัญหาของทรานซิสเตอร์ในวันนี้ ทรานซิสเตอร์เป็นหน่วยไฟฟ้าที่เล็กที่สุดที่สามารถผลิตขึ้นสำหรับชิ้นส่วนอิเล็กทรอนิกส์ ซึ่งเป็นส่วนประกอบทางไฟฟ้าที่ทำจากเซมิคอนดักเตอร์และบันทึกโดยเครื่องสแกนที่ล้ำสมัยอย่างไม่น่าเชื่อโดยใช้ความยาวคลื่นบนกระจก

โดยพื้นฐานแล้วมันคือสวิตช์ที่เชื่อมต่อระหว่างชั้นของซิลิกอนหลายสิบชั้น (ตามกฎทั่วไป) ที่มีขนาดเล็กมากและมีฟังก์ชันที่ชัดเจนมาก: เพื่อเปลี่ยนการไหลของกระแสที่ไหลผ่าน หลีกทางหรือตัดมัน การตัดหรือขั้นตอนแต่ละครั้งแสดงถึงศูนย์หรือหนึ่งในเลขฐานสองและเมื่อเวลาผ่านไปสิ่งที่ได้รับคือการปรับปรุงเพื่อให้เกิดความเร็วมากขึ้นในการเปลี่ยนสถานะพลังงานมากหรือน้อยสำหรับการเปลี่ยนแปลงดังกล่าวและประสิทธิภาพมากหรือน้อยเมื่อปล่อยให้ ผ่านปัจจุบัน

เรากำลังเข้าใกล้ขอบของเทคโนโลยีทรานซิสเตอร์

ตามที่เราคิดไว้แล้ว ทรานซิสเตอร์ทุกตัวมีชุดการออกแบบที่แตกต่างกันไปตามผู้ผลิต Intel มีวิสัยทัศน์ TSMC เหมือนกันและ ซัมซุง เหมือนกันมากขึ้น ดังนั้นแม้ว่าความก้าวหน้าทั้งหมดจะถูกคัดลอกมากหรือน้อย แต่การนำไปใช้และการปรับปรุงนั้นแตกต่างกัน

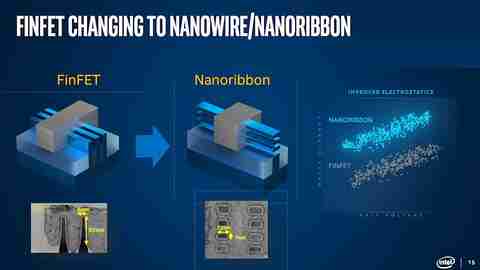

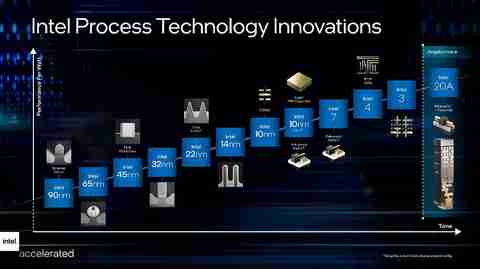

ทศวรรษที่ผ่านมา Intel ได้เปิดตัวทรานซิสเตอร์ FinFET ซึ่งได้รับการคัดเลือกจากผู้ผลิตทุกราย แต่การออกแบบนั้นกำลังจะสิ้นสุดลงด้วยเหตุผลหลายประการ ด้วยทรานซิสเตอร์ประเภทนี้ เรามีการออกแบบที่ยืดหยุ่นซึ่งปกติแล้วจะกว้าง ซึ่งมีประตูหลายบานข้ามผ่าน ทำให้ผู้ผลิตสามารถควบคุมการจัดการพลังงาน การเชื่อม และวัสดุก่อสร้างได้ดียิ่งขึ้น ตลอดจนลดขนาดต่อไปเป็นนาโนเมตร

ปัญหาหลักที่เรามีนั้นง่ายมาก คือไม่สามารถลดขนาดลงได้อีกมาก เนื่องจากเรามีพื้นที่จำกัดตามยาว และเกทของทรานซิสเตอร์แต่ละตัวไม่สามารถเชื่อมติดกันได้อีกต่อไปโดยไม่สูญเสียอิเล็กตรอน จำเป็นต้องเสริมด้วยว่าระยะห่างระหว่างกันนั้นเล็กมากจนการเชื่อมและการเชื่อมต่อต้องใช้วัสดุและโลหะผสมใหม่ที่มีราคาแพงอย่างมาก ซึ่งบางส่วนยังอยู่ในช่วงทดลองซึ่งรับประกันการผ่านของพลังงานและไม่ก่อให้เกิดราคา

ทางออกคืออะไร? ทรานซิสเตอร์ชนิดใหม่ที่ไม่เพียงแต่อนุญาตให้มีชั้นมากขึ้นในการขับเคลื่อนกระแส ปรับปรุงการควบคุม การเชื่อม และประสิทธิภาพ แต่ยังลดระยะห่างระหว่างทรานซิสเตอร์กับ Angstroms (หน่วยวัดระดับโมเลกุลและอะตอม)

RibbonFET โซลูชันของ Intel สำหรับขีดจำกัดใหม่ของการพิมพ์หิน

หากคุณไม่สามารถลดพื้นที่และควบคุมพารามิเตอร์ทั้งหมดโดยไม่ทำให้เกิดต้นทุน เหลือเพียงการตรวจสอบเส้นทางใหม่เท่านั้น เส้นทางใหม่นี้ในรูปแบบของสถาปัตยกรรมใหม่สำหรับทรานซิสเตอร์เรียกว่า GAA หรือที่เรียกว่า Gate-All-Around จากที่นี่ แนวคิดจะแบ่งออกเป็นสามด้านหรือ 4 ด้าน (ไม่ชัดเจนทั้งหมด):

- TSMC กาเฟต .

- ซัมซุง เอ็มบีซีเฟต .

- อินเทล ริบบิ้นFET .

- Global Foundries อยู่ในบริเวณขอบรกกับข่าวลือ แต่ไม่มีอะไรเป็นรูปธรรม

เกิดอะไรขึ้นที่นี่? เช่นเดียวกับที่เกิดขึ้นกับ FinFET GAA จะมีหลายตัวแปรทั้งหมดโดยใช้แนวคิดของทรานซิสเตอร์เดียวกัน เราได้พูดคุยกันเกี่ยวกับ Samsung MBCFET แล้ว GAAFET ยังไม่ถูกเปิดเผย แม้ว่าจะมาพร้อมกับ 2 nm ของบริษัทก็ตาม ดังนั้นหลังจากการนำเสนอของ Intel ในงาน Architecture Day 2021 และหลังจากเปิดเผยรายละเอียดเพิ่มเติมบางอย่างแล้ว เราก็จะได้รู้เดิมพันกัน ของยักษ์สีน้ำเงิน: RibbonFET

แนวคิดนี้เรียบง่าย แต่ยากที่จะนำไปใช้ พวกเขาใช้ทรานซิสเตอร์ที่มีความกว้างที่ยืดหยุ่นได้ ซึ่งจะลดลงเมื่อมีการกระโดดในการพิมพ์หินแต่ละครั้ง และอนุญาตให้หลายชั้น ซึ่งปัจจุบันเรียกว่านาโนชีต แผ่นแห้ง หรือครีบตามอุตสาหกรรม เพื่อเชื่อมต่อในแนวตั้งบนทรานซิสเตอร์แทนในแนวนอน บรรลุอะไร? อย่างแรกเลย ลดความกว้างของทรานซิสเตอร์ลงอย่างมาก อนุญาตให้มีแผ่นนาโนมากขึ้นบนพื้นผิวที่เล็กกว่า และเหนือสิ่งอื่นใดคือ Gate เดียวที่จะควบคุมพลังงานทั้งหมดของเซลล์

ไฟฟ้าสถิตได้รับการปรับปรุงอย่างมากตามที่ Intel แสดงให้เห็นในการนำเสนออย่างเป็นทางการ ซึ่งเราต้องดูขนาดของ Pitch Gate และ Gate Stack เท่านั้น มันเริ่มจาก 6 นาโนเมตร x 50 นาโนเมตร ถึง 12 นาโนเมตร x 7 นาโนเมตร และด้วยแผ่นนาโนควบคุมที่มากขึ้นและบัดกรีได้ดีขึ้น

การออกแบบนาโนชีตแบบแปรผันตามความต้องการของทรานซิสเตอร์

เห็นได้ชัดว่าและดังที่เราได้เห็นในเอกสารต่างๆ ตั้งแต่ Intel พูดถึงทรานซิสเตอร์ชนิดใหม่นี้ ดูเหมือนว่ายักษ์สีน้ำเงินสามารถรวบรวมจำนวนตัวแปรของนาโนชีตต่อทรานซิสเตอร์ได้

รายละเอียดนี้มีความสำคัญ เนื่องจากเมื่อ Intel พัฒนาการพิมพ์หินโดยใช้เครื่องสแกน EUV ที่ดีกว่า จะสามารถรักษาหมายเลขเดิมหรือลบหมายเลขที่ต้องการเพื่อเพิ่มประสิทธิภาพแต่ละ Gate ได้ เอกสารแสดงตั้งแต่ 2 ถึง 5 แต่ในแผ่นข้อมูลล่าสุด ตัวเลขกลมปรากฏเป็น 4 ครีบ / นาโนชีตเพิ่มเติมต้องการขั้นตอนเพิ่มเติมในการสร้างทรานซิสเตอร์ ดังนั้นจึงเพิ่มค่าใช้จ่ายของแต่ละชิป ดังนั้น Intel อาจเริ่มต้นด้วยตัวเลข วิธีการเหล่านี้จนกว่าคุณจะมีการปรับปรุงการแกะสลักและการควบคุมการผลิต วัสดุและรอยเชื่อมที่ช่วยให้คุณกำจัดแผ่นนาโนที่กำหนดจำนวนหนึ่งและลดต้นทุนโดยไม่กระทบต่อความเสถียร ความเร็ว หรือประสิทธิภาพของทรานซิสเตอร์

สิ่งนี้จะขึ้นอยู่กับความสูงของประตูตามหลักเหตุผลและด้วยจำนวนแผ่นที่เราสามารถติดตั้งได้เนื่องจากตอนนี้แทนที่จะถูกล้อมรอบด้วยสามไซต์เหมือนที่เกิดขึ้นใน FinFET ปลายแต่ละด้านล้อมรอบด้วย Gate โดยสิ้นเชิงซึ่งหมายความว่าหนึ่ง ด้านนั้นเหมาะสมที่สุด แต่อีกด้านหนึ่งทำให้ลดความสูงระหว่างแผ่นได้ยาก

Intel RibbonFET จะใช้ในชิปของตนเมื่อใด ตามข้อมูลของบริษัทเองในปี 2024 แน่นอนว่าภายในสิ้นปีเดียวกันนั้นหากทุกอย่างเป็นไปด้วยดี แม้ว่าหากเป็นการเดินเรือที่ราบรื่น เราก็จะได้เห็นมันภายในกลางปีเดียวกันนั้น ไม่ว่าในกรณีใดมันจะเป็นกระบวนการพิมพ์หิน 20A ที่รวมไว้และจะแข่งขันกับ GAAFET ของ TSMC และ MBCFET ของ Samsung . Intel มั่นใจมากว่าจะสร้างความแตกต่างที่ได้กล่าวไว้แล้วว่าจะเป็นผู้นำอุตสาหกรรมเซมิคอนดักเตอร์และเทคโนโลยีอีกครั้งในปี 2025 – ไม่ต้องสงสัยเลยว่าเป็นการประกาศเจตนา