ปัจจุบันอุตสาหกรรมเซมิคอนดักเตอร์ดำเนินการโดย บริษัท สามแห่งเท่านั้น: อินเทล, ซัมซุง และ TSMC การต่อสู้มุ่งเน้นไปที่พวกเขาทั้งสามคนและในอนาคตจะไม่มีมุมมองของคู่แข่งรายใหม่ดังนั้นใครก็ตามที่ก้าวหน้าเร็วกว่าจะพาแมวไปที่น้ำ เราคาดหวังอะไรจากปีนี้? ใครจะครองตลาดและจะลากผู้ผลิตจำนวนมากที่สุดไว้ใต้ตัก มาทบทวนแผนผังองค์กรและการวางแผนของ กระบวนการพิมพ์หินของทั้งสามคน

ดังที่เราได้เห็นแล้วในบทความอื่น ๆ ในเรื่องนี้อุตสาหกรรมเผชิญกับความท้าทายหลายประการในระยะสั้นและระยะยาว ครั้งแรกของสิ่งเหล่านี้คือไม่ต้องสงสัยว่านาโนเมตรจะลดลงเพื่อให้ได้ความหนาแน่นที่สูงขึ้น, ความถี่ที่สูงขึ้นและการบริโภคที่น้อยลงหรือเท่ากัน แต่หลังจากนี้ก็มีคนอื่น ๆ

การเปลี่ยนทรานซิสเตอร์เป็นก้าวแรกสู่ยุคใหม่

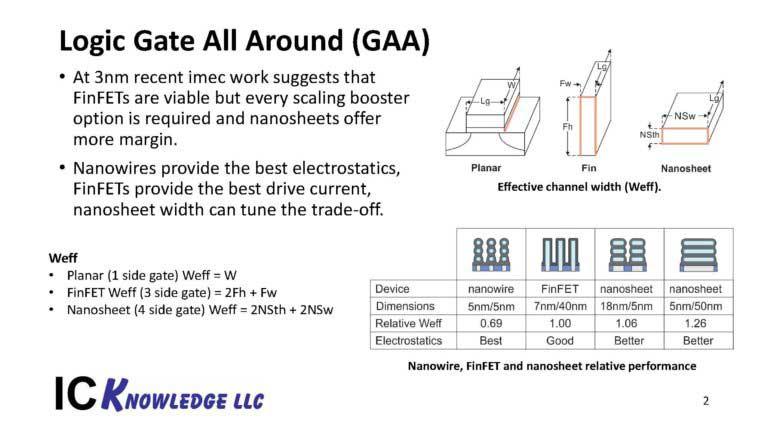

สิ่งที่เราได้พูดคุยแล้วและเป็นกุญแจสำคัญในการทำความเข้าใจบทความนี้ดังนั้นเราจะไม่ไปไกลเกินไปที่นี่ ยุค FinFET กำลังจะสิ้นสุดลงส่วนใหญ่เป็นเพราะวิธีที่พวกเขาสร้างขึ้นด้วยสามประตูของพวกเขาในสามด้านของทรานซิสเตอร์ เท่าที่พวกเขาเป็นทรานซิสเตอร์ 3 มิติการลดลงของนาโนเมตรและด้วยพื้นที่ที่สามารถอยู่ระหว่างพวกเขาบังคับให้อุตสาหกรรมละทิ้งพวกเขาเพื่อให้ได้ความหนาแน่นที่สูงขึ้น

ตัวสำรองของมันมีชื่อและกำลังใช้งานอยู่: Gate All Around หรือ GAA หรือที่เรียกว่า HNS สำหรับการใช้งาน nanoblades แนวนอนที่รวมเข้าด้วยกันซึ่งเป็นความแปลกใหม่ที่สำคัญในทรานซิสเตอร์ประเภทนี้

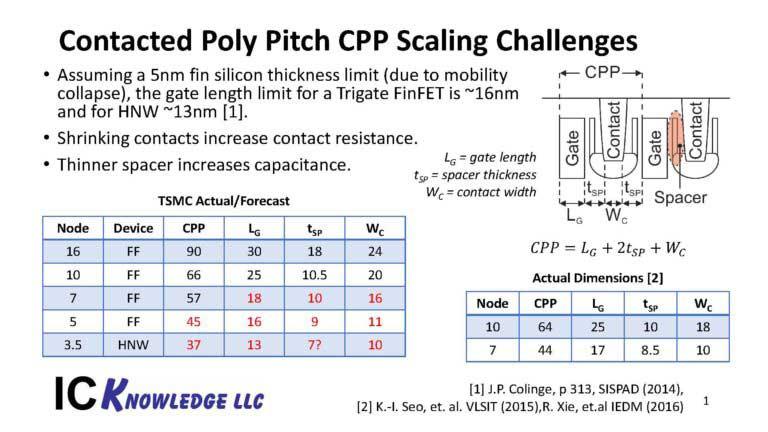

ในรุ่นใหม่นี้ nanolayers จะแคบมากพวกเขาปรับปรุง nanowires และ electrostatics ดังนั้นความยาวของประตูจะลดลงจาก 16 nm ใน FinFET เป็น 13 nm (หรือน้อยกว่า) ใน GAA ซึ่งขึ้นอยู่กับโดยตรง Poly Pitch (CPP) ที่ติดต่อ นั่นคือ CPP ที่ต่ำกว่าเท่ากับความหนาแน่นที่สูงขึ้นโดยตรรกะที่บริสุทธิ์

ในระยะสั้นปัญหาที่นี่คือ บริษัท ขนาดใหญ่ทั้งสามกำลังเข้าใกล้นี้ในเวลาที่ต่างกัน: TSMC จะไม่ดำเนินการจนกว่าอย่างน้อย 3 นาโนเมตร Samsung จะมีการผลิตที่ 5 นาโนเมตรและ Intel ไม่ได้ให้ข้อมูลเกี่ยวกับเรื่องนี้ .

ลดครีบสำหรับทรานซิสเตอร์แต่ละตัวเพื่อประหยัดพื้นที่

การซ้อนกันของใบไม้และประตูจะมีผลกระทบโดยตรงอีกอย่างหนึ่งเมื่อนาโนเมตรยังคงลดลงและไม่มีใครอื่นนอกจากการลดลงของครีบหรือครีบ สิ่งนี้มีความเกี่ยวข้องโดยตรงกับการควบคุมกระแสการส่งผ่านของทรานซิสเตอร์เนื่องจากวิศวกรเหลือพื้นที่น้อยและมีตัวเลือกเพื่อให้ได้กระแสคงที่และลดการรั่วไหล

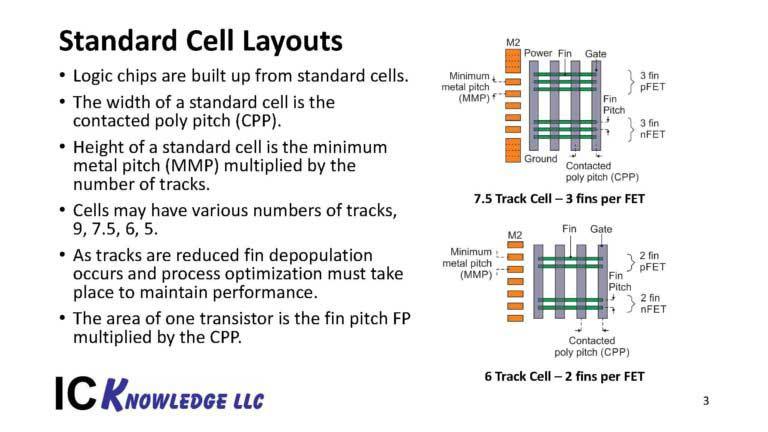

ทั้งหมดนี้มุ่งเน้นไปที่เซลล์ซึ่งเป็นส่วนพื้นฐานของการทำความเข้าใจว่า GAAs จะทำงานอย่างไร เซลล์เหล่านี้มีพื้นฐานมาจาก แทร็ค ซึ่งจะลดลงด้วยการพิมพ์หินแต่ละครั้งเพื่อปรับปรุงความหนาแน่นและกับพวกเขา ระยะห่างระหว่างโลหะขั้นต่ำ (MMP)

จำนวนเซลล์ที่น้อยลงจะลดทั้งพื้นที่แนวตั้งและแนวนอนและด้วยเหตุนี้ส่วนประกอบทั้งหมดที่ประกอบขึ้นจึงต้องลดลงทำให้ยากต่อการนำทรานซิสเตอร์ไปใช้

ดังนั้นขั้นตอนต่อไปของ GAA (HNS) จึงเรียกว่า CFET หรือ FET เสริม . มันเป็นขั้นตอนต่อไปในแง่ของความสามารถในการปรับความหนาแน่นเนื่องจากมีคุณสมบัติ FET ซ้อนกันสองประเภท: nFET และ pFET

ความแตกต่างกับ Nanoblades ใน GAA คือพวกเขามีความสูงที่แตกต่างกันสองระดับซึ่งเมื่อเซลล์ถูกลดจำนวนลง CFETs เพิ่มเติมสามารถชดเชยได้มากขึ้นซึ่งตอนนี้ประตูอยู่ในแนวดิ่ง ฟินพิช สามารถลดได้มากขึ้นเรื่อย ๆ ระหว่างแต่ละ CFET

เหตุผลนี้มีผลกระทบต่อเสถียรภาพที่ยังคงต้องศึกษา เราไม่ทราบว่าการดำเนินการของแต่ละคนจะเป็นอย่างไรในท้ายที่สุดหรือพวกเขาวางแผนที่จะแก้ปัญหาเช่นการเชื่อมโยงระหว่างกัน (บทความพิเศษในหัวข้อนี้ในไม่ช้า) แต่การปรับปรุงดั้งเดิมนั้นมีความสามารถที่เรามั่นใจว่าเป็นหนทาง (จาก 1, 4X ถึง 2X ในการออกแบบที่ดีที่สุด)

อนาคตสำหรับกระบวนการพิมพ์หินในปี 2020, 2021 และ 2022

แม้ว่าดูเหมือนว่าอุตสาหกรรมจะมีแผนการในอนาคตในระยะยาว แต่ความจริงก็คือพวกเขามีความยุติธรรมมากพอ ๆ กับเวลา ด้วยเหตุผลนี้และการเห็นทั้งหมดข้างต้นและบทความที่กำลังจะมาถึงเราต้องคิดว่าอนาคตเป็นวันนี้มากที่สุดสามปีและมีคำถามมากมายที่อาจมีผลต่อการเปลี่ยนแปลงเล็กน้อยในข้อกำหนดที่รั่วไหลออกมา .

สิ่งที่เรากำลังพยายามจะพูดคือถ้าสิ่งนี้ในตัวเองเกือบจะวิ่งข้ามอุตสาหกรรมในโพสต์ของล่วงหน้าเราต้องเข้าใจว่ากระบวนการพิมพ์หินขยายเวลาแน่นอนเพราะอุตสาหกรรมต้องทำงานเป็นเวลานานเพื่อแก้ปัญหาต่อไปนี้เพื่อ ลงไปอีกนาโนเมตร

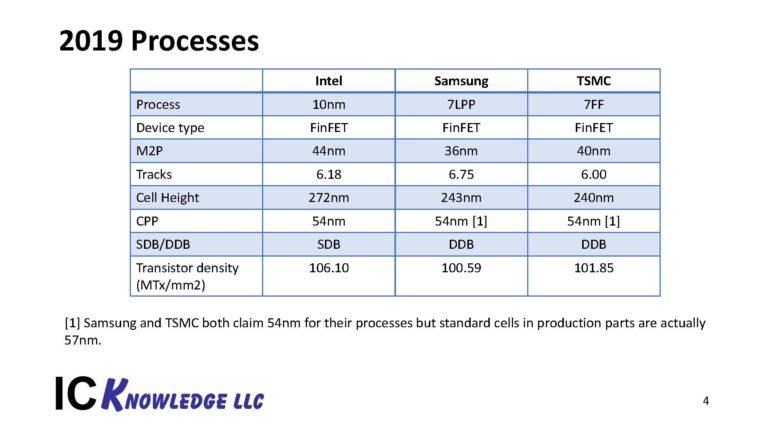

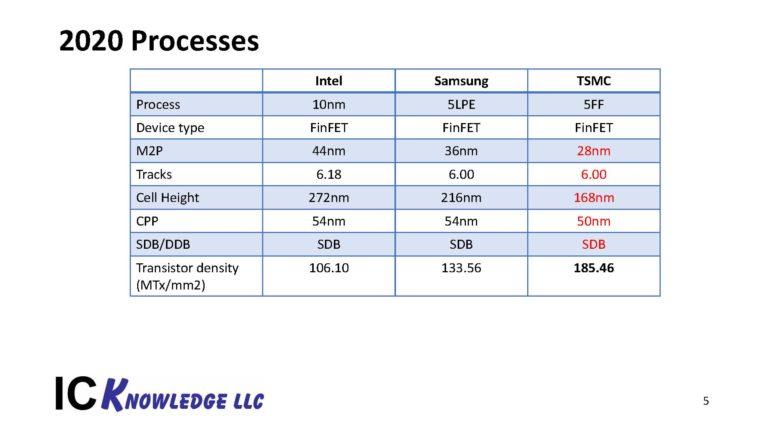

แนวโน้มนี้จะขยายออกไปจนถึงปี 2030 ซึ่งเป็นไปได้ว่าเรามีการรอบอะตอมและที่นั่นเราจะเผชิญกับปัญหาต่อไปนี้อีกครั้ง ในขณะเดียวกันเมื่อมองย้อนกลับไปที่จุดเริ่มต้นที่ชัดเจนในปี 2019 Intel ได้เปิดตัว 10nm, Samsung 7nm LPP และ TSMC 7nm FF

ที่นี่จะต้องมีการชี้แจงว่าถึงแม้ว่า Intel จะเป็นผู้นำด้วยกระบวนการพิมพ์หิน แต่ข้อดีนี้ไม่ได้เป็นเช่นนี้เนื่องจากรุ่นประสิทธิภาพสูงไม่พร้อมใช้งานดังนั้นทุกอย่างจึงเป็นเรื่องสมมติขึ้นมา

แม้ว่า Intel ที่มีขนาด 10 nm จะมีความหนาแน่นสูงกว่า แต่ปี 2020 จะไม่เป็นปีที่จะเปิดตัวเช่นนี้ในภาคส่วนใดก็ตามเนื่องจาก บริษัท ตั้งใจที่จะเพิ่มขึ้นเป็น 10 nm ++ ในปี 2021

ปี 2020 ทุกอย่างจะเปลี่ยนไปอย่างมากและแม้ว่า TSMC 5 นาโนเมตร ไม่ได้ถูกกำหนดด้วยความหนาแน่นอย่างไม่น่าเชื่อที่แท้จริงของ 185 ล้านทรานซิสเตอร์ต่อ mm2 ความจริงก็คือพวกเขาจะไม่เข้าโดยตรงกับผลิตภัณฑ์ที่มีประสิทธิภาพสูงเช่นเดียวกับที่เกิดขึ้นกับ Intel ในปี 2019

ซัมซุงสำหรับส่วนของมันจะตามมาด้วยการปลุกของ TSMC ด้วยกระบวนการที่มีความหนาแน่นน้อยกว่า แต่มีผลกำไรมากขึ้นต่อเวเฟอร์ Intel ที่ไม่มีการปรับปรุงบนขอบฟ้าและมองที่ 2021

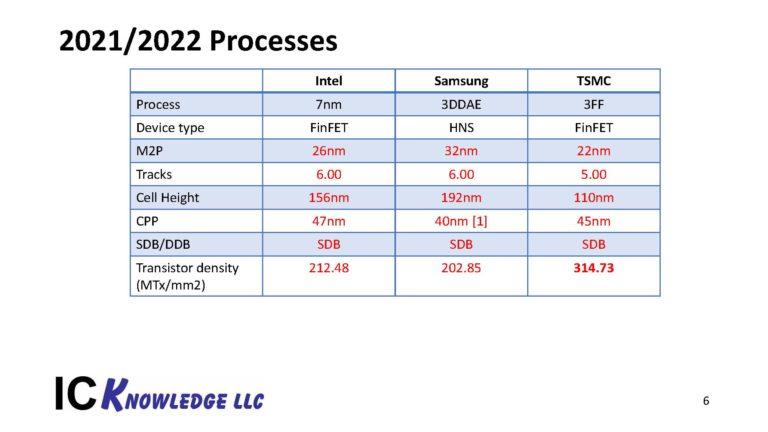

เมื่อพูดอย่างเหมาะสมก็จะต้องชี้ให้เห็นว่าแม้ว่า บริษัท จะยืนยันสิ่งที่ปรากฏในกราฟ แต่ความจริงก็คือมันจะยากมากที่จะเห็นผลิตภัณฑ์ในกระบวนการพิมพ์หินกล่าวว่านอกเหนือจากที่พวกเขาผลิตมวล นั่นคือเหตุผลที่ปี 2022 ถูกพูดถึงว่าเป็นปีแห่งการดำเนินการที่เป็นไปได้

Intel อาจพร้อมใช้งาน 7nm ภายในสิ้นปี 2021 แต่ TSMC จะแทบไม่มี 3FFs สำหรับปีนั้นไม่ว่าในกรณีใดก็ตามที่มองถึงปี 2022 เนื่องจากพวกเขากำลังประสบกับปัญหาที่พวกเขาต้องแก้ไขก่อน

แต่ Samsung อาจมี 3 นาโนเมตร HNS ภายในสิ้นปีนั้นและเพื่อดูผลิตภัณฑ์ขั้นสุดท้ายในต้นปี 2022 ซึ่งสามารถแข่งขันกับ Intel ได้ในระดับที่มากหรือน้อย ไม่ว่าในกรณีใดอุตสาหกรรมนี้กำลังเปลี่ยนแปลงไปอย่างมากซึ่งอาจมีความล่าช้าเกิดขึ้นดังนั้นเราจะเฝ้าดูการเปลี่ยนแปลงตามเวลาจริงของกระบวนการพิมพ์หิน