プロセッサが従うプロセスとは何か疑問に思ったことがある場合は、 RAM この記事では、PCのXNUMXつの最も重要な要素間の通信プロセスがそれぞれと通信するものを説明するため、データと実行する必要のある命令を取得するために割り当てられていることを確認してください。その他。

この記事で どのタイプのRAMが優れているかについては説明しません or それぞれの仕様 、ただし、プロセッサはプログラムを実行できるように通信します。

その理由 外部メモリを使用します というのは 情報を格納するために必要なトランジスタの量は、プロセッサのスペースに収まりません 、そのため、プロセッサの外部にあるRAMメモリを使用して、実行する命令とデータを格納する必要があります。

プロセッサがRAMとの通信を必要とするのはなぜですか?

の段階 CPU RAMから実行する次の命令は「フェッチ」と呼ばれ、命令サイクルを構成するXNUMXつのステージのXNUMXつです。フェッチ-デコード-実行。これについては、最初の記事のこの記事でのみ説明します。結果を書き戻すことを除いて、RAMメモリがそれらに介入しないため、XNUMXつは別の時間に残されます。

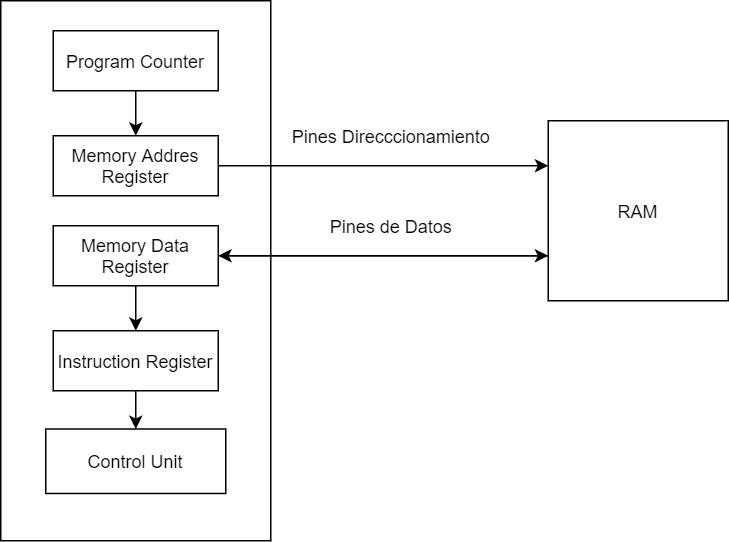

すべてのプロセッサには、次の命令をキャプチャするのに役立つ一連のレジスタが相互に接続されています。これらは次のとおりです。

- プログラムカウンター: PCは、次のプロセッサ命令が配置されている次のメモリラインを指します。 その値は、完全な命令サイクルが完了するたび、またはジャンプ命令がプログラムカウンタの値を変更するたびに1ずつ増加します。

- メモリアドレスレジスタ: MARは、PCのコンテンツをコピーし、RAMのアドレスピンに配線されているCPUのアドレスピンを介してRAMに送信します。

- メモリデータレジスタ :命令が読み取られると、RAMはデータバスを介して、MARがポイントしていたメモリアドレスの内容を送信します。

- 命令レジスタ: 命令は命令レジスタにコピーされ、そこから制御ユニットが命令を復号化して、命令の実行方法を認識します。

DRAMメモリとは何ですか?

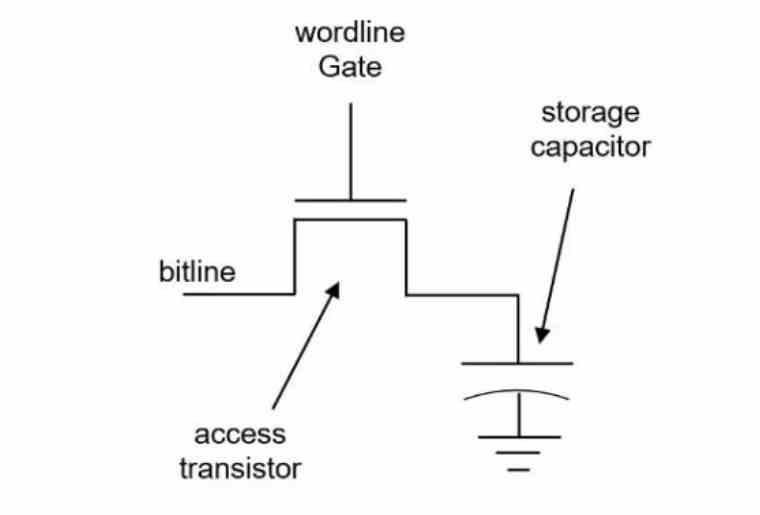

RAMに使用されるメモリの種類 、システムRAMとビデオRAMまたはVRAMの両方として、 DRAMまたは1T-DRAMメモリ 。 このタイプのメモリでは、各ビットは コンデンサとトランジスタの組み合わせ 、SRAMのようないくつかのトランジスタの代わりに、1T-DRAMという名前が付けられました。

現在PCで使用されているすべてのRAMメモリ:DDR4、GDDR6、HBM2e、LPDDR4など。これらはDRAMタイプのメモリですが、プロセッサ、レジスタキャッシュ、スクラッチパッドの内部メモリはSRAMタイプです。

コンデンサとトランジスタの上記の組み合わせは、 ビットセル , ビットセルのコンデンサが充電されている場合、そのビットセルに含まれている情報は1であると解釈され、充電されていない場合、0であると解釈されます。

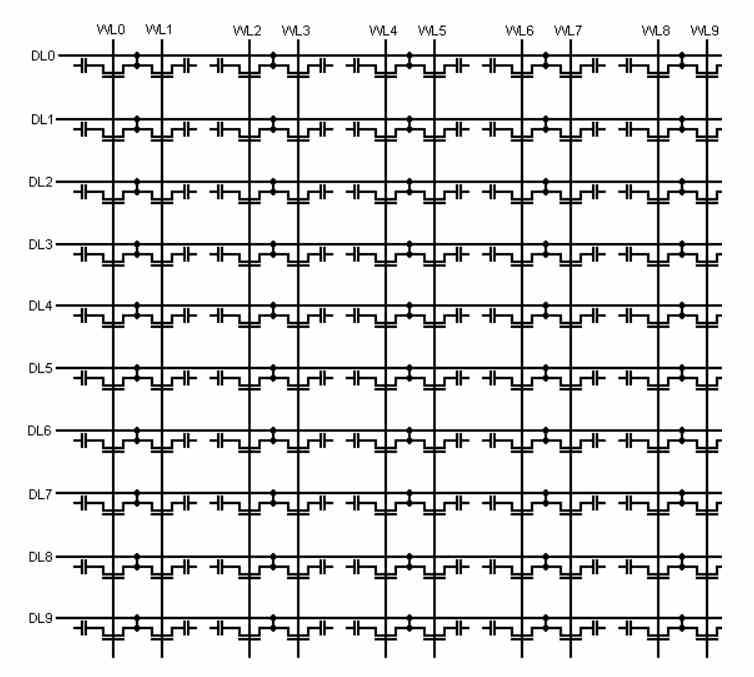

ビットセルは、次のようにアドレス指定ピンを使用してアクセスするマトリックスに編成されています。

- ビットの前半は、アクセスする行を選択します

- アドレス指定ビットの後半には、アクセスする列が含まれています。

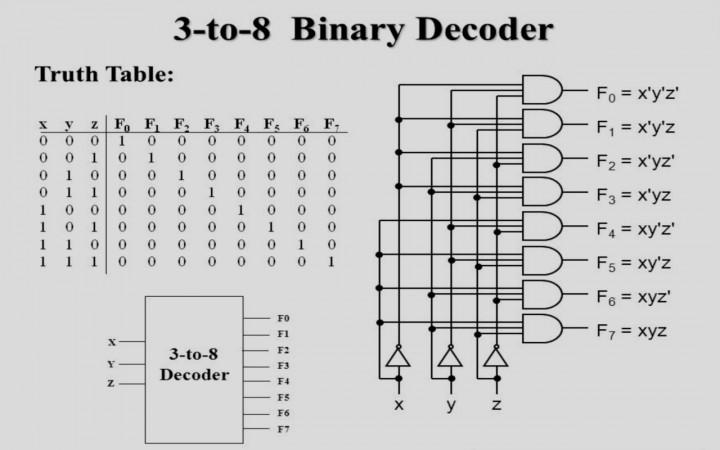

このために、ビットセルのマトリックスとアドレス指定バスの間にバイナリデコーダがあり、適切なビットセルを選択できます。

RAMと通信するための接点ピン

RAMにアクセスするには、 CPUは、CPUがコンテンツにアクセスできるようにする一連のピンを使用します。 RAM そしてそれを修正する 。 これを行うには、最初にデータがどこにあるか、またはデータを操作する場所を見つけてから、特定の方向に送信する必要があります。 これには、XNUMXつの異なるタイプのピンが使用されます。

- アドレッシング ピン : 通常、A0からANまでマークされます。ここで、Nはピンの数であり、アドレス指定ビットの数に等しく、常に2 ^ Nです。

- データピン :RAMとの間でデータが送受信される場所です。

- 書き込み有効: ピンがアクティブな場合、データ転送はメモリに向けて行われ、書き込みが行われます。一方、ピンがアクティブでない場合、データ転送はプロセッサに向けて行われ、読み取りが行われます。

システムに複数のRAMメモリチップがある場合、アドレス指定の最初のビットを使用して、DIMMメモリモジュール内でアクセスするメモリチップを選択します。 アドレスピンとデータピンが同じ場合もあります。 これは、データのアドレス指定とアクセスが同時に行われないためです。

しかし、アドレス指定がどのように機能するかをより正確に理解するには、基本的な電子機器であるバイナリデコーダーを確認する必要があります。

バイナリデコーダとRAMとの通信におけるその役割

バイナリデコーダは非常に一般的な電子機器であり、nビットの入力から2 ^ n個の異なる可能性から入力が選択されるという点で構成されています。 これは、n個のNOTゲートを2 ^ n個のANDゲートに配置することによって構築されます。

バイナリデコーダは非常に一般的な電子機器であり、nビットの入力から2 ^ n個の異なる可能性から入力が選択されるという点で構成されています。 これは、n個のNOTゲートを2 ^ n個のANDゲートに配置することによって構築されます。

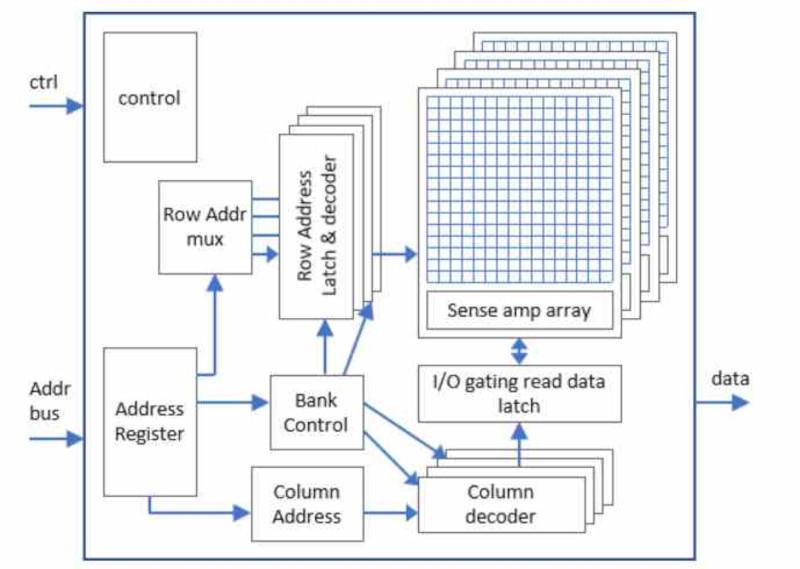

RAMメモリでは、アドレス指定はXNUMXつのサイクルで送信されます。最初にアクセスされる行が送信され、次に列が送信されます。同時にではありません。

この理由は非常に簡単な説明です。16つのRAMメモリチップに16個のアドレス指定ビットが接続されたプロセッサがあるとします。 バイナリデコーダが16ビットの場合、65536個のNOTゲートと8個のANDゲートが必要になります。 対照的に、8ビットのバイナリデコーダには256つのNOTゲートとXNUMXのANDゲートがあり、実装がはるかに簡単です。

これが、RAMへのアドレス指定がXNUMX段階で行われる理由です。

メモリバンク

RAM内のデータは 連続して保存されない 、ただし、同じチップ内の異なるバンクでは、 各バンクにはビットセルの配列が含まれています ただし、たとえばnビットのデータを送信する場合は、ビットセルの配列がn個必要になり、それぞれがデータバスのピンに接続されます。

の用法 複数の銀行 、同じメモリチップ内で、 メモリへのXNUMX回のアクセスで同時に複数のビットを選択できます 、以来、 すべての銀行がアドレス指定を共有します 。 したがって、8つのメモリバンクがある場合、特定のビットセルを選択すると、8つのメモリバンクとの間で同時にデータが送受信されます。

RAMメモリのバンクの標準サイズは8ビットであるため、アドレス指定の最大メモリは常に2 ^ nバイトとしてカウントされます。 実際には、16、32、64ビットバスなどです。それらが行うことは、最初から始まるいくつかの連続するメモリアドレスのデータを送信することです。

RAMとCPU間の通信

CPUとRAMの間の通信は、正しく行われていること、つまり、正しいデータが正しい方向に正しいメモリバンクで送信されているかどうかに依存します。 したがって、すべてのRAMメモリには機会のウィンドウがあります。これは、さまざまな操作を実行できる時間です。これらは特定の時間に実行し、このプロセスに従う必要があります。

- 列を選択(アドレス指定)

- 行を選択(アドレス指定)

- データ伝送。

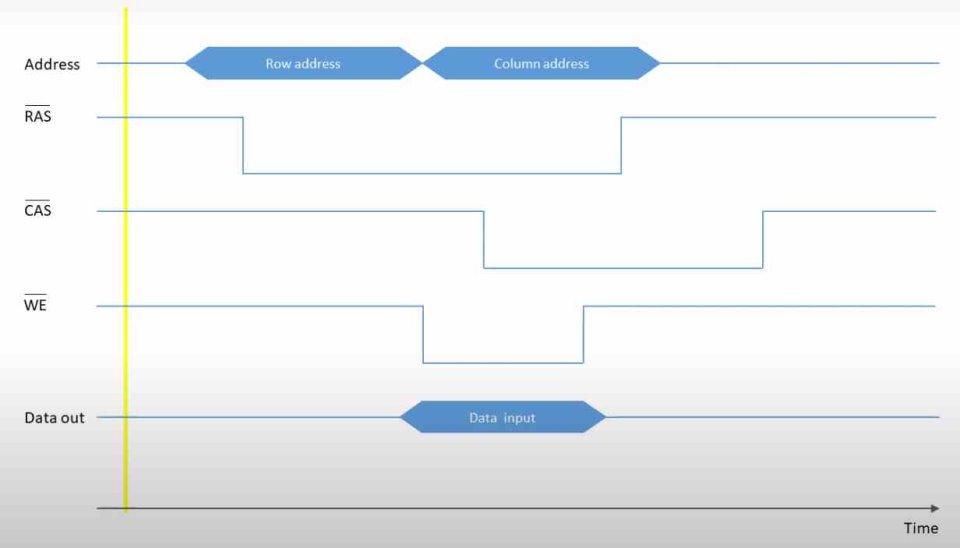

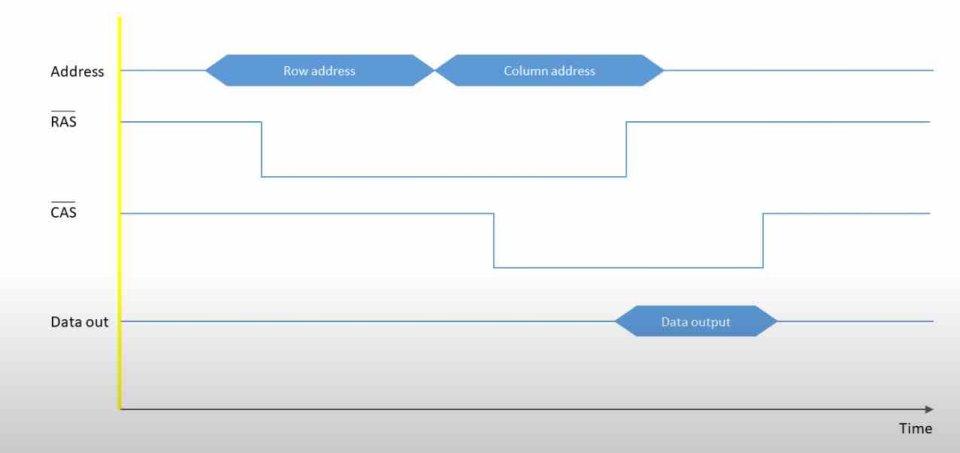

このために、一連の特別なピンが使用されます。そのうちのXNUMXつはすでに見ており、書き込み可能ですが、他のXNUMXつは次のとおりです。

- カラムアクセスストロボ: このピンは、アクセスする列を示していることをRAMメモリに示すとアクティブになります。

- 行アクセスストロボ:: このピンは、アクセスしたい行を示していることをRAMメモリに示すとアクティブになります。

両方の操作は次のように要約できます。

- 読み取り操作は非常に簡単です。このため、データがRAMからプロセッサに送られることを示し、行と列を示して、情報がメモリRAMからプロセッサに向かって流れるように、WEピンを非アクティブにする必要があります。 。

- 書き込み操作は多少異なります。このため、WEピンはアクティブである必要がありますが、データはデータ列を選択した後ではなく、行が選択された後、データが配置されている列の選択と同時に送信されます。

これにより、プロセッサとそのRAM間の通信がどのように機能するかについての大まかなアイデアをすでに得ることができます。