Intel machen AMD haben den Einsatz von 3DIC-Technologien aller Art zum Bau zukünftiger Prozessoren angekündigt, ein Trend, der in den kommenden Jahren zunehmen wird. Aber wie könnten zukünftige Intel- und AMD-CPUs mit dieser Technologie gebaut werden? In diesem Artikel werden wir versuchen zu beleuchten, wie diese Prozessoren der Zukunft sein könnten.

Wenn neue Fertigungsknoten verwendet werden, kann man sehen, wie die Kosten immer mehr steigen. Dies zwingt nicht nur dazu, neue Strategien hinsichtlich des Designs neuer Prozessoren zu entwickeln, sondern auch neue Wege, diese zu bauen.

Was verstehen wir unter 3DIC?

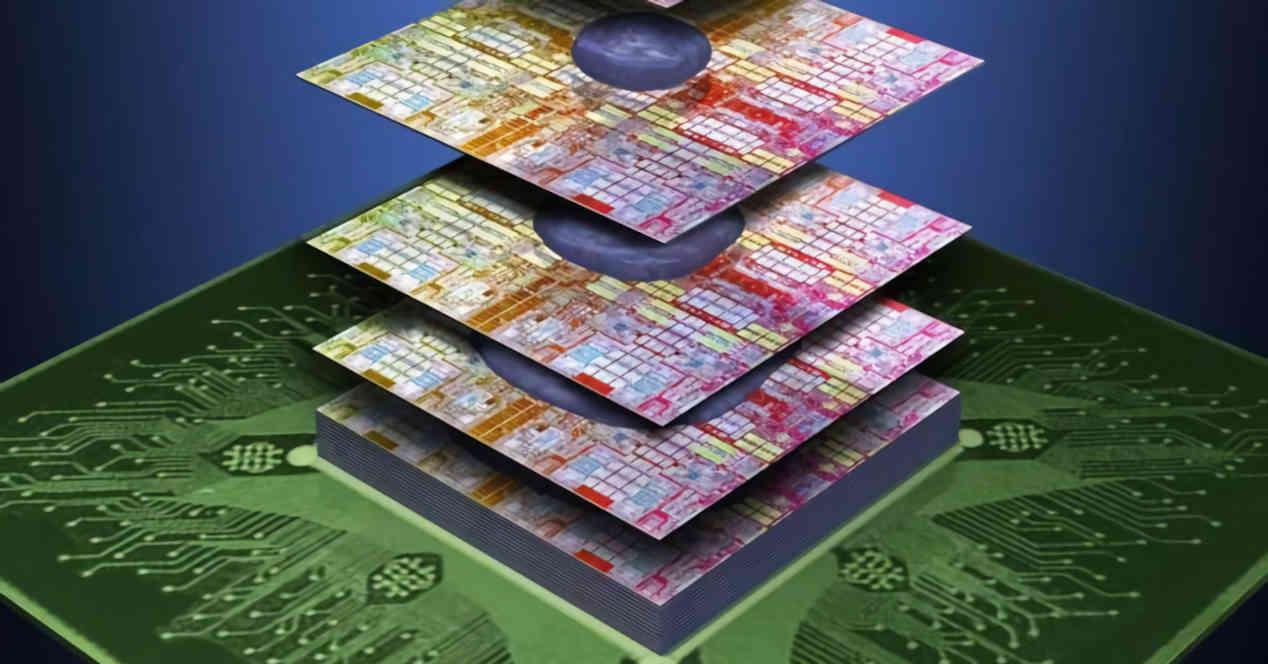

3DIC ist das Akronym für eine dreidimensionale integrierte Schaltung. Dies ist der Name, der allen Prozessoren oder Sätzen derselben gegeben wird, die aus mehreren verschiedenen Chips bestehen, die unter Verwendung von Durchkontaktierungen über Silizium oder TSV miteinander verbunden sind. Bisher haben wir auf dem Markt für PC-Hardwarekomponenten den 3D-NAND-Speicher verschiedener Marken sowie die verschiedenen Generationen von HBM-Speicher nur als Demonstrationen gesehen

Einer der Vorteile des 3DIC besteht darin, dass wir mehrere Chips mit unterschiedlichen Fertigungsknoten kombiniert verwenden können. Dies ist ein Vorteil, da nicht alle Elemente eines Prozessors auf einen neuen Fertigungsknoten skaliert werden müssen, da sie keine bieten eine höhere Leistung für sie.

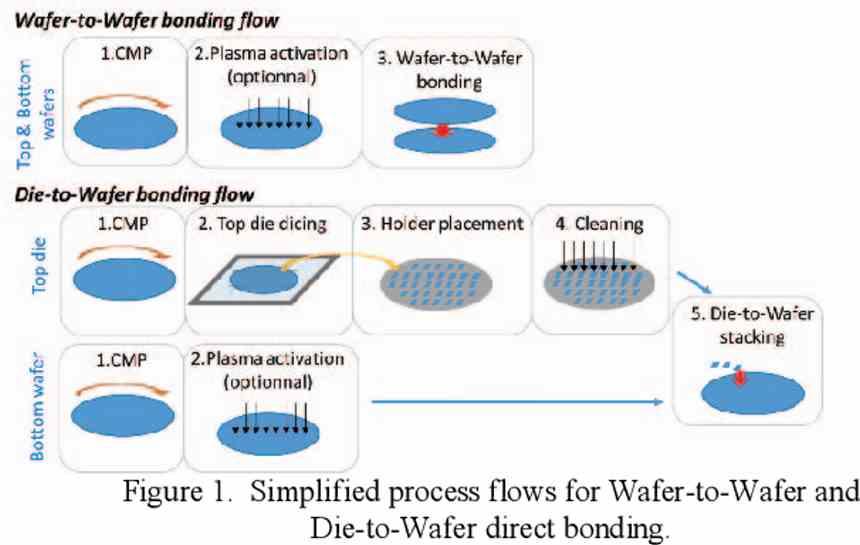

Direktes Die-to-Die-Verfahren oder Erstellen eines komplexen Prozessors mithilfe von 3DIC

Die Idee, zwei Logikchips eins zu eins in einer 3DIC-Struktur unter Verwendung einer vertikalen TSV-Verbindung zu verbinden, hat das Potenzial, alle Sektoren der Prozessorindustrie vollständig zu verändern. Von den SoCs mit sehr geringem Stromverbrauch, die als Zentralprozessor in Ihrem Telefon dienen, bis zu den auf Rechenzentren spezialisierten High-End-Chips.

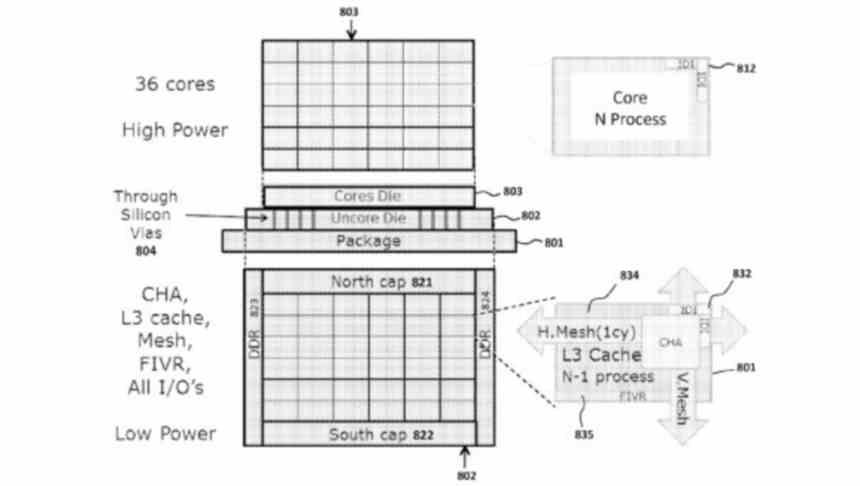

Die Idee, einen Prozessor in zwei oder mehr vertikal ausgerichtete Teile zu trennen, haben wir bereits im Intel Lakefield gesehen, in dem der CPU Kerne und die Northbridge sind auf verschiedenen Chips von der Southbridge getrennt und verwenden Fertigungsknoten. anders. Wir sollten uns jedoch einige Modelle von SoCs und sogar CPUs ansehen.

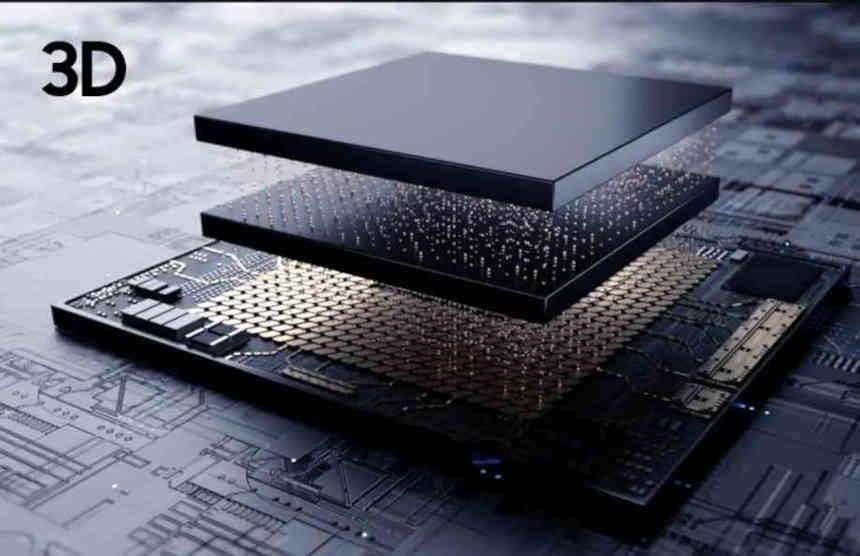

Die Intel-Architektur ist jedoch nicht die einzige Möglichkeit, eine moderne CPU mithilfe der 3DIC-Technologie zu erstellen, sondern es gibt auch eine andere Art der Konfiguration, bei der die CPU-Kerne und das „Uncore“ desselben Prozessors in zwei oder mehr verschiedene Chips getrennt sind, die über miteinander verbunden sind TSV.

Die größte Herausforderung für CPU-Architekten im Moment sind die Energiekosten für die Datenübertragung im Prozessor, die in einer Konfiguration, über die wir sprechen, stark reduziert sind. Daher wird der 3DIC nicht nur die zukünftige Wette von Intel und AMD sein, sondern auch auch etwas, das wir in der sehen werden ARM Welt.

Ein möglicher zukünftiger 3DIC-Prozessor von Intel oder AMD

In unserem Beispiel nehmen wir als Beispiel die Desktop-Prozessoren, die auf Zen 2 und Zen 3 basieren und die Kerne des Uncore teilen, ein Element, das auch als Northbridge bekannt ist, obwohl AMD es Scalable Data Fabric nennt. Wir werden diese Architektur verwenden, da sie eine sehr klare Aufteilung der Komponenten aufweist.

AMD oder Intel könnten einen zukünftigen Prozessor herausbringen, bei dem wir scheinbar eine monolithische Konfiguration sehen würden, aber eigentlich ein 3DIC-Prozessor, bei dem sich der Uncore auf einem anderen Chip im Stack befindet als die verschiedenen Kerne.

Dies würde bedeuten, dass die Konnektivität zwischen den CCDs oder Chiplets mit dem SDF nicht nur direkter und daher mit geringerer Latenz wäre, sondern auch weniger verbrauchen würde, da AMD oder Intel eine größere Anzahl von verwenden könnten Pins mit einer niedrigeren Geschwindigkeit, jedoch ohne Bandbreitenverlust, um die verschiedenen Kerne mit dem Rest des Prozessors zu kommunizieren, was wiederum eine erhebliche Steigerung der Leistung pro Watt der verschiedenen CPUs ermöglicht.

Die Idee, die Prozessoren in mehrere Ebenen zu unterteilen, ermöglicht es beispielsweise, Mehrkernsysteme zu erstellen, die über 8 Kerne auf demselben Chip hinausgehen, und alle mit einer ausreichenden Geschwindigkeit miteinander zu kommunizieren, wobei die Latenz gut ist und im Vergleich zu aktuellen Modellen nur sehr wenig Energie verbraucht wird.

Welche Nachteile haben Intel und AMD bei der Bereitstellung des 3DIC?

Der größte Kompromiss sind die enormen Kosten für die Herstellung eines 3DIC-Prozessors, die zusätzliche Herstellungsschritte erfordern. Der größte Kompromiss ist jedoch das sogenannte thermische Abwürgen, das auftritt, wenn zwei Komponenten so nahe beieinander liegen, dass die Temperatur einer Komponente erreicht wird. Dies wirkt sich auf die Leistung eines anderen aus und ermöglicht es Komponenten nicht, die Taktraten zu erreichen, die sie separat und sogar in einer 3DIC-Konfiguration erreichen könnten.

Dies macht diese Konfigurationen auch zu viel komplexeren und teureren Kühlsystemen, die sie zusammen von Heimsystemen entfernen und sie ideal für Server aller Art machen. Paradoxerweise sind sie jedoch auch die Zukunft von SoCs für PostPC-Geräte. Sie sind in ihrer Größe begrenzt und können nicht mehr horizontal erweitert werden, so dass sie dies nur vertikal tun können.

Der Grund dafür ist, dass mit jedem neuen Knoten nicht nur die Kosten für jeden Wafer-Millimeter im Quadrat steigen, sondern es auch zunehmend schwieriger wird, immer größere Prozessoren ohne eine gefährliche Ausfallrate zu bauen. All dies wird die meisten Designs dazu zwingen, von einem riesigen monolithischen Chip zu einem aus mehreren vertikalen Chips bestehenden zu werden, nur weil die Kosten pro Wafer so hoch sind, dass selbst die hohen Kosten der 3DIC-Herstellung kein Hindernis darstellen.