VLIW ย่อมาจาก Very Long Instruction Word ซึ่งแปลว่าคำสั่งที่ยาวมาก ในโลกของสถาปัตยกรรมโปรเซสเซอร์ใช้เพื่อกำหนดประเภทของ ซีพียู หรือโปรเซสเซอร์ที่บรรลุคำสั่งแบบขนานหรือ ILP แต่มีวิธีการที่แตกต่างจากที่ใช้ในโปรเซสเซอร์ superscalar ซึ่งเป็นวิธีที่ใช้กันทั่วไปในซีพียู

ซีพียูประเภท VLIW มีข้อดีและข้อเสียหลายประการเมื่อเทียบกับโปรเซสเซอร์อื่น ๆ และไม่เพียง แต่ใช้ในซีพียูเท่านั้น แต่ยังเป็นหน่วย shader สำหรับ GPU และใน DSP ด้วย

ปัจจุบันการออกแบบ VLIW ดูเหมือนจะหายไปจากฮาร์ดแวร์ของพีซี แต่ก็ยังคงเป็นตัวเลือกที่ถูกต้องในการออกแบบโปรเซสเซอร์ใหม่สำหรับพื้นที่ต่างๆของตลาดฮาร์ดแวร์แม้ว่าจะเลิกใช้ไปแล้วก็ตาม

โปรเซสเซอร์ VLIW ทำงานอย่างไร

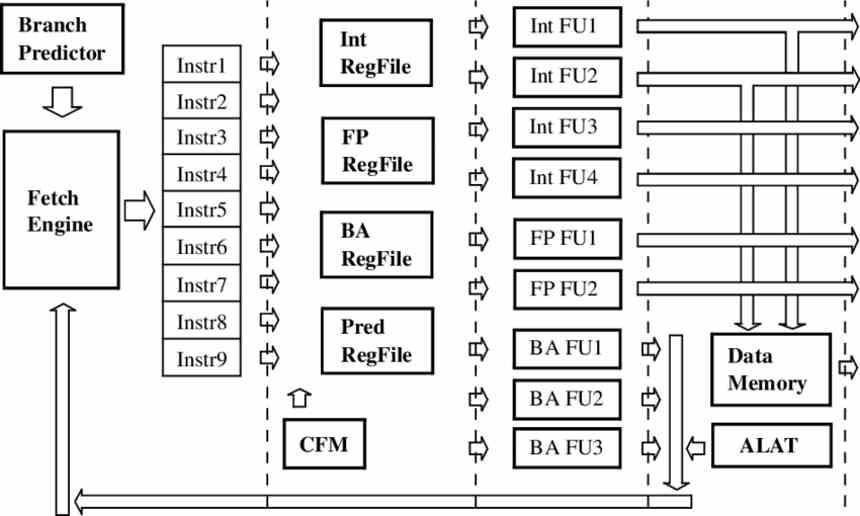

ในโปรเซสเซอร์ superscalar หรือ ILP แบบเดิมคำแนะนำจะถูกบันทึกและประมวลผลทีละรายการในระหว่างรอบการเรียนการสอนของแต่ละคำสั่ง ไม่ว่าเรากำลังพูดถึงการดำเนินการตามคำสั่งหรือนอกคำสั่ง ในกรณีของโปรเซสเซอร์ VLIW สิ่งที่ต้องทำคือการจัดกลุ่มคำสั่งต่างๆให้เป็นหนึ่งเดียวและส่งเข้าด้วยกันไปยังหน่วยต่างๆที่มีอยู่ในโปรเซสเซอร์

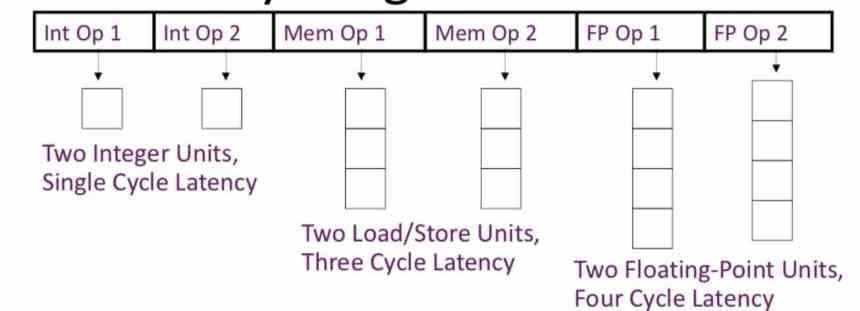

เพื่อให้บรรลุนี้ โปรเซสเซอร์ VLIW ขึ้นอยู่กับคอมไพเลอร์เป็นอย่างมากเมื่อสร้างรหัสไบนารี ซึ่งจะจัดกลุ่มคำสั่งที่แตกต่างกันเป็นคำสั่งเดียวโดยคำนึงถึงระดับอาชีพของหน่วยประมวลผลแต่ละหน่วยในแต่ละช่วงเวลาของการดำเนินการเสมอ การดำเนินการซึ่งจะขึ้นอยู่กับจำนวนรอบนาฬิกาที่ต้องการโดยแต่ละคำสั่ง

เนื่องจากคำแนะนำอาจมีองศาของระยะเวลาที่แตกต่างกันในแง่ของรอบนาฬิกานี่จึงเป็นปัญหาด้านประสิทธิภาพเนื่องจากในหลายรอบนาฬิกาเราจะมีหน่วยการดำเนินการที่ไม่ต้องทำอะไรเลยและจะดำเนินการตามคำสั่ง NOP ซึ่งหมายความว่าในช่วงนาฬิกานั้น รอบเครื่องดังกล่าวไม่ได้ดำเนินการใด ๆ สิ่งนี้ทำให้โปรเซสเซอร์ VLIW ต้องพึ่งพาคอมไพเลอร์เป็นอย่างมากเพื่อให้ได้ประสิทธิภาพสูงสุด

ข้อดีและข้อเสียของการออกแบบ VLIW

ข้อดีส่วนใหญ่ที่นำมามีดังต่อไปนี้:

- ฮาร์ดแวร์ที่รับผิดชอบในการถอดรหัสคำสั่งนั้นง่ายกว่าซีพียู ILP หรือ TLP มากซึ่งช่วยให้มีพื้นที่ว่างบนชิปสำหรับหน่วยประมวลผลมากขึ้นและทำให้สามารถดำเนินการคำสั่งได้มากขึ้นในเวลาเดียวกัน

- การมีพื้นที่มากขึ้นยังช่วยให้คุณสามารถวางรีจิสเตอร์ได้จำนวนมากขึ้นซึ่งเหมาะอย่างยิ่งสำหรับการอำนวยความสะดวกในการดำเนินการเชิงเก็งกำไรโดยทั่วไปของโปรเซสเซอร์ที่ไม่ได้สั่งซื้อโดยไม่ต้องใช้บัฟเฟอร์การจัดเรียง

เกี่ยวกับข้อเสียประการแรกคือในความจริงที่ว่าจำเป็นต้องใช้คอมไพเลอร์ที่ซับซ้อนกว่านี้อย่างที่สองคือสิ่งที่เราเคยพูดถึงมาก่อนและนั่นขึ้นอยู่กับความจริงที่ว่ามีการเสียหน่วยประมวลผลที่แตกต่างกันมากขึ้น เนื่องจากพวกเขาส่วนใหญ่จะใช้เวลาว่างอย่างมีความสุข

เพื่อให้เข้าใจได้ดีขึ้นลองนึกภาพว่าคุณได้จัดกลุ่มคำสั่ง VLIW 3 ซึ่งต้องใช้ 4 รอบแรกในการดำเนินการ 7 รอบที่สองและ 10 รอบที่สาม หน่วยประมวลผลที่รับผิดชอบในการดำเนินการคำสั่งแรกจะเป็น 6 รอบนาฬิกาโดยไม่ต้องทำอะไรเลย 3 ตัวที่สองและทั้งหมดนี้เนื่องจากหน่วยที่สามจะต้องใช้ 10 รอบในการทำงาน

ในทางกลับกันเราต้องเพิ่มความจริงที่ว่าแม้ว่าในระดับคำสั่งไบนารีจะไม่เปลี่ยนแปลง แต่เมื่อพัฒนา CPU ใหม่เป็นไปได้ว่าคำสั่งที่มีอยู่แล้วจะเพิ่มหรือลดจำนวนรอบ สิ่งนี้ทำให้คอมไพเลอร์ที่แตกต่างกันจำเป็นสำหรับการทำซ้ำใหม่ของโปรเซสเซอร์ใหม่ซึ่งทำให้การเรียกใช้ตัวประมวลผลเวอร์ชันขั้นสูงขึ้นเป็นเรื่องยากและในหลาย ๆ กรณีจำเป็นต้องสร้างไบนารีเป็นไบนารีคอมไพเลอร์ซึ่งจัดลำดับคำสั่งใหม่สำหรับ CPU ใหม่

การสร้างคำสั่งโดยคอมไพเลอร์

เพื่อให้คุณเข้าใจได้ดีขึ้นเราได้เตรียมรายการไว้สองสามรายการรายการแรกคือการดำเนินการในโปรเซสเซอร์ superscalar หรือที่เรียกว่า ILP ส่วนที่สองคือ CPU ประเภท VLIW

เริ่มต้นด้วยโปรเซสเซอร์ประเภท ILP รายการคำแนะนำจะเป็นดังต่อไปนี้:

- โหลด A1

- โหลด B1

- โหลด A2

- ชาร์จ B2

- คูณค่า A1 และ B1

- เพิ่มค่าของ A2 และ B2

- เพิ่ม A1 และ A2

- ขนส่งสินค้า A3

- โหลด B3

- คูณ A3 ด้วย B3

- เพิ่ม B1 และ B2

ในทางกลับกันโปรเซสเซอร์ VLIW จะจัดกลุ่มคำสั่งหลายคำสั่งไว้ในที่เดียว:

- A2 และ B2 จะชาร์จพร้อมกัน

- โหลด A2 และ B2 คูณ A1 และ B1 เพิ่ม A2 และ B2

- โหลด A3, B3, คูณ A3 ด้วย B3 และเพิ่ม B1 และ B2

ความจริงที่ว่าเราได้จัดการเพื่อจัดกลุ่มคำสั่ง 11 คำให้เป็นเพียง 3 คำสั่งที่มีขนาดใหญ่มากหมายความว่าระยะเวลาที่คำสั่ง VLIW แต่ละคำสั่งจะต้องใช้ส่วนใหญ่จะเป็นเวลาที่ใช้สำหรับคำสั่งที่ซับซ้อนที่สุดในกลุ่มคำสั่ง

การเข้าถึงหน่วยความจำของโปรเซสเซอร์ประเภทนี้

ดังที่เราได้กล่าวไปก่อนหน้านี้โปรเซสเซอร์ VLIW ขึ้นอยู่กับคอมไพเลอร์และหลายครั้งที่พวกเขาเพิ่มคำสั่ง NOP ลงในโค้ดระหว่างการคอมไพล์ เหตุผลในการทำเช่นนี้เนื่องจากการสร้าง VLIW CPU ที่มีคำสั่งขนาดตัวแปรนั้นซับซ้อนมากดังนั้นการสร้างบิตขนาดคงที่ซึ่ง CPU จะอ่านคำแนะนำและดึงข้อมูลจำนวนนั้นจากหน่วยความจำในแต่ละรอบ . และคำแนะนำ

ซึ่งหมายความว่าโปรเซสเซอร์ VLIW ต้องการบัสข้อมูลที่กว้างกว่าซีพียูทั่วไปเนื่องจากมีการจัดกลุ่มบิตจำนวนมากในแต่ละครั้งที่รวบรวมคำสั่งใหม่เพื่อดำเนินการ นี่เป็นส้นเท้า Achilles ที่ยอดเยี่ยมเนื่องจากในโปรเซสเซอร์ ILP ซึ่งพบได้ทั่วไปในซีพียูพีซีความกว้างของข้อมูลที่แคบลงและใช้ตัวควบคุมหน่วยความจำที่ง่ายกว่า

สิ่งปกติในโปรเซสเซอร์ VLIW คือพวกเขากำลังรวบรวมคำสั่งต่อไปนี้เพื่อดำเนินการในขณะที่กำลังดำเนินการคำสั่ง VLIW ปัจจุบัน เนื่องจากการจัดกลุ่มคำสั่งหลาย ๆ คำสั่งเข้าด้วยกันทำให้เวลาในการจับภาพของแต่ละคำสั่งแยกจากกันจึงลดลง