ในขณะที่ชิปสร้างเทคโนโลยีโหนดและ กฎของมัวร์ กำลังชะลอตัวลงอย่างเห็นได้ชัดผู้ผลิตชิปและนักออกแบบยังคงแสวงหาโซลูชันใหม่ที่สร้างสรรค์เพื่อให้การปรับขนาดอุปกรณ์และประสิทธิภาพเพิ่มขึ้นอย่างต่อเนื่อง เทคโนโลยีการห่อหุ้มขั้นสูงเป็นหนึ่งในพื้นที่ที่เราได้เห็น นวัตกรรมที่ยอดเยี่ยม ในช่วงไม่กี่ปีที่ผ่านมาเช่นการเปิดตัวซิลิคอน ผู้แทรกสอด การรวมหน่วยความจำ HBM บนชิปเองหรือการเปลี่ยนไปสู่การแยกส่วนด้วยชิปเล็ต วันนี้เราจะมาพูดคุยกับคุณเกี่ยวกับ เทคโนโลยี LSI ของ TSMC ซึ่งพวกเขาตั้งใจที่จะสร้างชิปของพวกเขาในอนาคตและสิ่งที่สามารถเปลี่ยนแปลงได้ - เพื่อให้ดีขึ้น - วิธีการทำงานของอุตสาหกรรมนี้

ตัวแทรกซิลิกอน ก่อให้เกิดความท้าทายด้านต้นทุนเนื่องจากมีราคาแพงมากและต้องการซิลิกอนจำนวนมากในขณะที่การออกแบบชิปเล็ตโดยใช้บรรจุภัณฑ์แบบเดิมบนพื้นผิวอินทรีย์ถูก จำกัด ด้วยแบนด์วิดท์อินพุต / เอาต์พุตและประสิทธิภาพการใช้พลังงาน ทางออกหนึ่งของปัญหานี้คือการแนะนำอุตสาหกรรมของเมทริกซ์ซิลิกอนระดับกลางที่เชื่อมต่อชิปลอจิกสองตัวเข้าด้วยกัน แต่จะอยู่ในขอบเขตที่ จำกัด และไม่ใช้รอยเท้าเดียวกันกับตัวแทรกซิลิกอนแบบเต็ม อินเทลEMIB ของ (Embedded Die Interconnect Bridge) ได้รับการพูดถึงมากที่สุดเกี่ยวกับการนำเทคโนโลยีนี้ไปใช้เมื่อเร็ว ๆ นี้

TMSC LSI จะเป็นอนาคตของชิปอุตสาหกรรมหรือไม่?

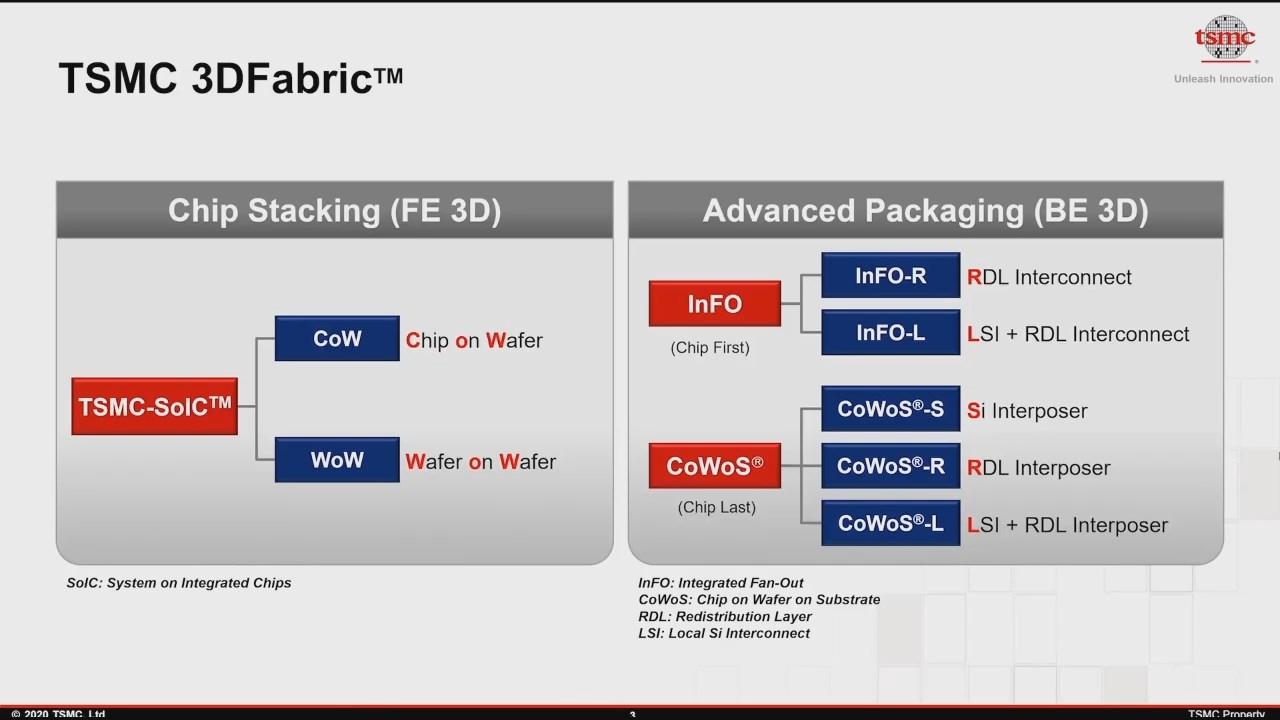

ในระหว่างการประชุมวิชาการเทคโนโลยี 2020 ของ TSMC ผู้ผลิตชาวไต้หวันได้ให้รายละเอียดเกี่ยวกับรูปแบบของเทคโนโลยีดังกล่าวที่เรียกว่า Local Si Interconnect (LSI) ซึ่งจะนำเสนอสำหรับเทคโนโลยีการห่อหุ้ม InFO และ CoWoS ในรูปแบบของ InFO-L และ CoWoS-L

ความก้าวหน้าใหม่นี้เป็นส่วนหนึ่งของสิ่งที่ TSMC เรียกมันในตอนนี้ ผ้า 3D เทคโนโลยีการบรรจุซึ่งนำเสนอตัวเลือกการห่อหุ้มและการรวมที่ค่อนข้างหลากหลายซึ่งรวมถึง SoIC, InFO และ CoWoS

คำอธิบายสั้น ๆ สำหรับผู้อ่านของเราที่ไม่คุ้นเคยกับคำเหล่านี้: โซไอซี (System on Chip Integrated) เป็นเทคโนโลยีการรวมชิปแบบไฮบริดและการรวมชิปซ้อนของ TSMC ซึ่งช่วยให้สามารถเรียงซ้อนกันของชิปหลายอาร์เรย์เข้าด้วยกันทำให้ความกว้างของวงดนตรีสูงมากและมีจุดต่อระหว่างแม่พิมพ์ของซิลิกอนที่ใช้พลังงานต่ำ ปัจจุบันเทคโนโลยีนี้ไม่มีใครเทียบได้ในอุตสาหกรรม

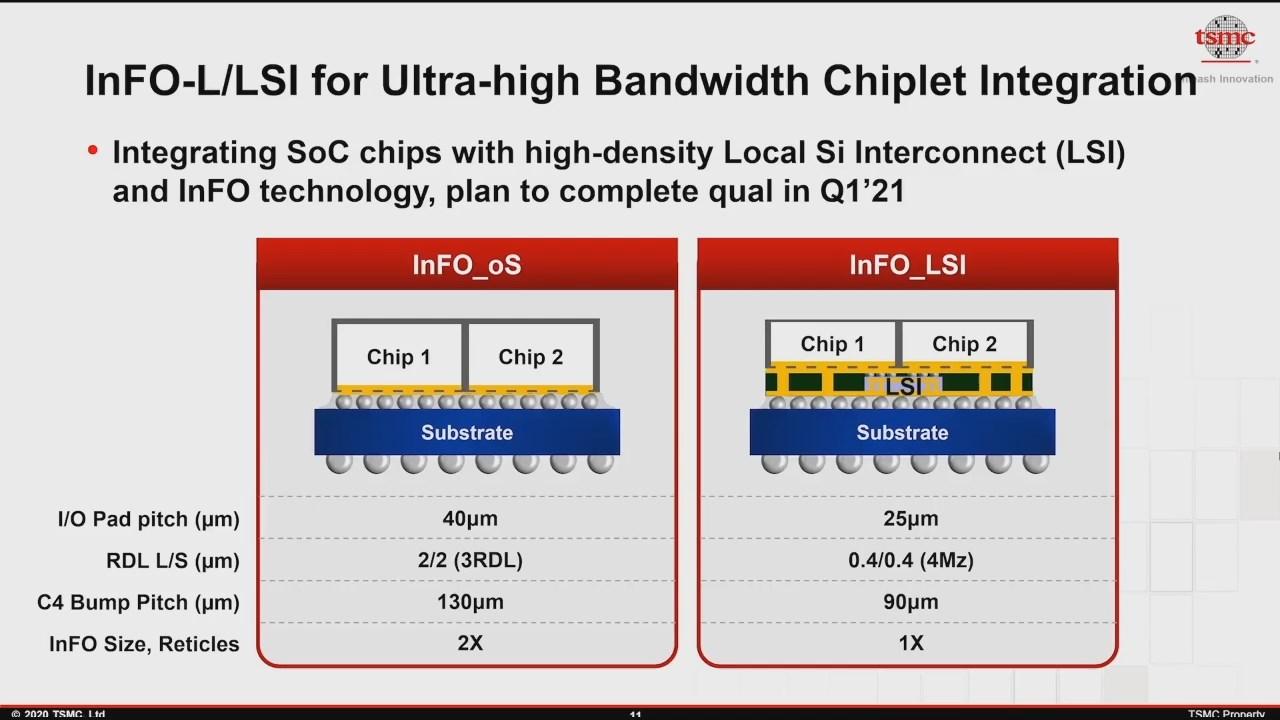

InFO เป็นเทคโนโลยีการบรรจุพัดลมหรือการห่อหุ้มของ TSMC ซึ่งแม่พิมพ์จะถูกนำออกจากเวเฟอร์ซิลิกอนและวางไว้บนเวเฟอร์ตัวพาอื่นซึ่งมีโครงสร้างที่ใหญ่กว่าเช่นทองแดง RDL (redistribution layer) และตามมาด้วยสารตั้งต้นของผู้ขนส่ง

ตัวแปร TSMC ของ InFO ที่มีการรวม LSI เรียกว่า InFO-L หรือ InFO-LSI และเป็นไปตามโครงสร้างที่คล้ายกันโดยมีการเพิ่มใหม่ของชิปคนกลางที่เชื่อมต่อระหว่างซิลิคอนภายในสำหรับการสื่อสารระหว่างชิปทั้งสอง

CoWoS (Chip-on-Wafer-on-Substrate) ของ TSMC เดิมอธิบายว่าเป็นเทคโนโลยีการบรรจุหีบห่อแบบซิลิกอน 2.5D ของ บริษัท ซึ่งปัจจุบันยังอยู่ภายใต้ข้อกำหนด CoWoS-S แต่ในระหว่างนี้ยังครอบคลุมเทคโนโลยีการห่อหุ้มอื่น ๆ ด้วย ตามคำอธิบายระบุไว้ว่า RDL ถูกสร้างขึ้นเป็นอันดับแรกบนพื้นผิวฐานและขั้นตอนสุดท้ายคือชิปซิลิกอนที่เพิ่มเข้าไปในชุด

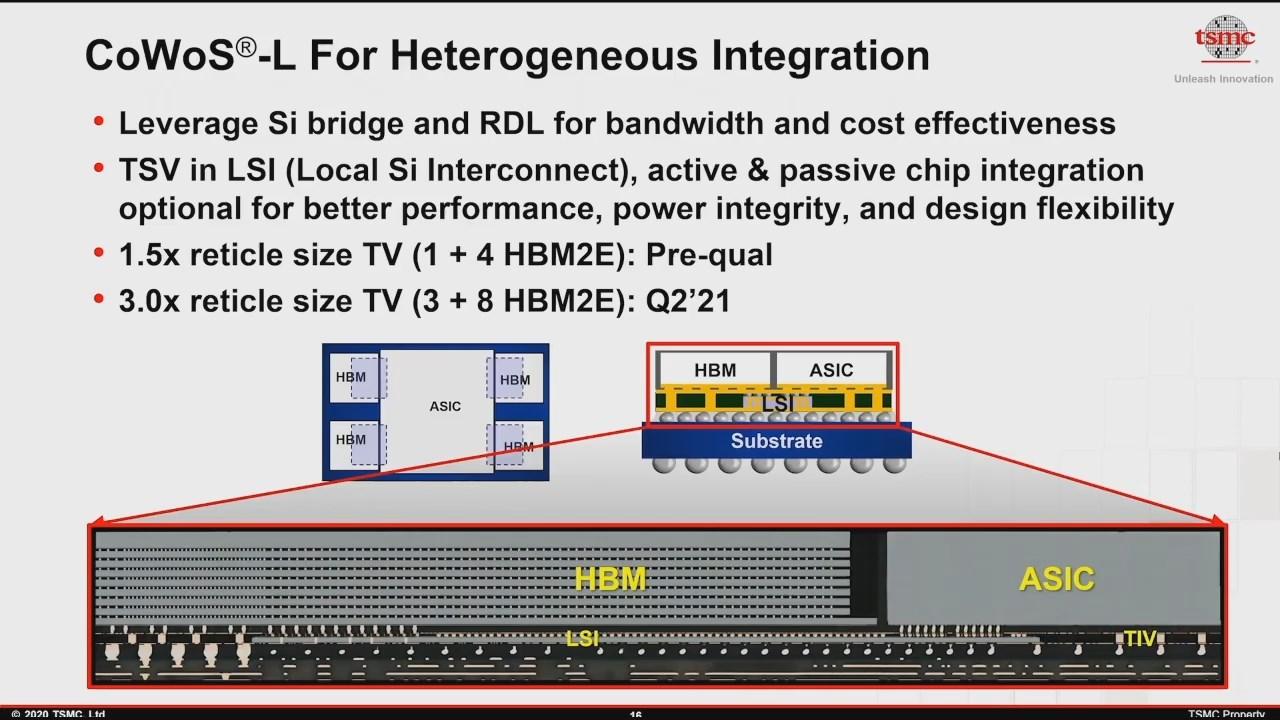

CoWoS-L เป็นรูปแบบใหม่ของเทคโนโลยีบรรจุภัณฑ์ชิปของ TSMC โดยเพิ่มการเชื่อมต่อระหว่างซิลิคอนในท้องถิ่นที่ใช้ร่วมกับ RDL ทองแดงเพื่อให้ได้แบนด์วิดท์ที่สูงกว่าการใช้บรรจุภัณฑ์ RDL (CoWoS-R) และยังมีต้นทุนที่ต่ำกว่าหากใช้ตัวประสานซิลิกอนเต็มรูปแบบ (CoWoS-S) กล่าวอีกนัยหนึ่งด้วยเทคโนโลยีการห่อหุ้มนี้คุณจะได้รับ ประสิทธิภาพที่ดีขึ้นในต้นทุนที่ต่ำลง .

TSMC อธิบาย LSI ว่าเป็นชิปแบบแอคทีฟหรือพาสซีฟ (ขึ้นอยู่กับความต้องการของผู้ออกแบบชิปและงบประมาณ) โรงหลอม TSMC คาดว่าจะเสร็จสิ้นการรับรองคุณสมบัติ InFO-L ในไตรมาสแรกของปี 2021 ในขณะที่ CoWoS-L อยู่ในกระบวนการตรวจสอบคุณสมบัติเบื้องต้นในขณะนี้ เทคโนโลยีการเชื่อมต่อระหว่างสะพานซิลิกอนเช่น LSI และ EMIB คาดว่าจะส่งมอบการออกแบบชิปที่มีประสิทธิภาพสูงในราคาที่ถูกลงสำหรับทั้งนักออกแบบและผู้บริโภค

กล่าวโดยย่อ: ชิปที่มีประสิทธิภาพสูงกว่าและราคาถูกกว่าสิ่งที่ควรแปล (สำหรับผู้ใช้) เป็น โปรเซสเซอร์ที่ทรงพลังและราคาถูกกว่า .