Apple ได้ขัดข้องในการส่งมอบ TSMC 5nm และได้เห็นประสิทธิภาพของ A14 และ Kirin 9XXX ในอนาคตซึ่งในทั้งสองกรณีประสิทธิภาพแทบจะไม่ได้ลดลงการบริโภคแทบจะไม่ลดลงเลยและโดยทั่วไปการปรับปรุงดูเหมือนจะน้อยกว่าที่คาดไว้ คำถามเกี่ยวกับอากาศแปรปรวน N5 TSMC ล้มเหลวหรือไม่? อะไรจะ เอเอ็มดี จะทำอย่างไรหากเวอร์ชันประสิทธิภาพสูงไม่บรรลุการปรับปรุงที่คาดไว้?

TSMC สามารถพูดได้ว่ามันประสบความสำเร็จด้วย 7 นาโนเมตรในทุกพื้นที่เนื่องจากเป็นโหนดดาวของช่วงเวลาในหลายภาคส่วน แต่ N5 ของพวกเขาดูไม่ดีนักโดยเฉพาะอย่างยิ่งถ้าเราคำนึงถึงการวัดของ SoC จำนวนมากเช่น Apple และ หัวเว่ย, เกิดอะไรขึ้น?

การปรับปรุงเล็กน้อยมากในกระบวนการที่มีประสิทธิภาพไม่สูง

ภาพที่เห็นใน A14 ทำให้เราสงสัยว่าเกิดอะไรขึ้นกับ Apple? เมื่อคำถามเป็นเช่นนั้นเกิดอะไรขึ้นกับไฟล์ ทีเอสเอ็มซี N5s เหรอ? การปรับปรุงชิป Apple ซึ่งเป็นเอกสิทธิ์เฉพาะครั้งแรก ARM เวอร์ชันที่มีโหนดพิเศษไม่แพ้กันทำให้เราเย็นชา ไม่ใช่ว่าชิปจะแย่ในตัวเองเพราะมันไม่ได้เป็นแบบนั้น แต่การปรับปรุงเมื่อเทียบกับ A13 หลังจากที่สถาปัตยกรรมเปลี่ยนไปและการเพิ่มขึ้นของนาโนเมตรทำให้เรานึกถึงประสิทธิภาพที่สูงขึ้นมากในทุกด้าน

ปัญหาดูเหมือนจะมาจาก EUV ซึ่งจำนวนเลเยอร์ที่สูงขึ้นอาจขัดขวางสิ่งที่ผู้เรียนไม่ได้คิดว่าเป็นปัญหาและไม่มีอะไรมากไปกว่าการได้รับประสิทธิภาพที่ดีขึ้นและประสิทธิภาพที่สูงขึ้น ในอดีตที่ผ่านมา Apple มักจะอวดอ้างถึงการเข้าถึงอย่างน้อยที่สุด 90% ของ ตามทฤษฎี ของโหนดที่ใช้งานได้ แต่กับ A14 ยังไม่มีการตรวจสอบจนกว่าจะมีการถาม

ปรากฎว่าหลังจากการสัมภาษณ์บางครั้ง A14 ที่ 5 นาโนเมตรก็ทำได้สำเร็จเท่านั้น ความหนาแน่นของทรานซิสเตอร์ที่มีประสิทธิภาพ 78% ซึ่งหมายถึงการสูญเสียทั้งหมดอย่างร้ายแรงในชิปทั้งหมด

เรากำลังเผชิญกับความล้มเหลวของโหนด N5 เพื่อดำเนินการต่อใน FinFET หรือไม่?

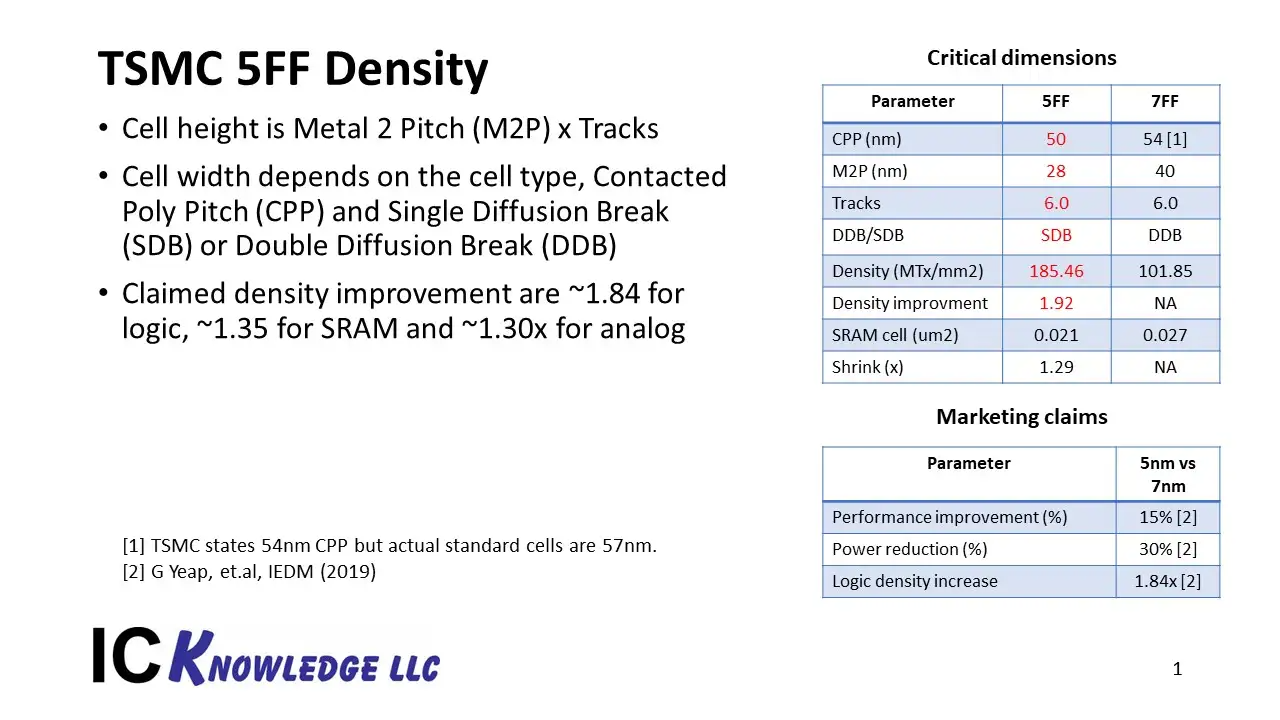

ไม่ชัดเจนจริงๆอาจเป็นจำนวนเลเยอร์สูงสุดอาจเป็นไปได้ว่า FinFET ไม่ได้รับการปรับให้เหมาะสมกับ EUV อีกต่อไปและเลเยอร์ที่มากขนาดนั้นหรืออาจเป็นไปได้ว่า Apple ไม่ได้ปรับให้เข้ากับโหนด ไม่ว่าในกรณีใดต้องจำไว้ว่า TSMC พูดถึงการลดลง 1.84X แต่ A14 นั้นต่ำกว่า 1.49X

อินเทล และ ซัมซุง กำลังทำงานร่วมกับ GAA บนแผ่นนาโนและ TSMC กำลังใช้ FinFET จนถึงขีด จำกัด ของอายุการใช้งานที่ 3 นาโนเมตร หาก 5nm เป็นโหนดการเปลี่ยนแปลงและตัวแปรประสิทธิภาพสูงจะประสบปัญหาเดียวกันบางที AMD ควรคิดใหม่โดยใช้โหนดนี้หากไม่มีการเปลี่ยนแปลงที่สำคัญเทียบกับ 7 นาโนเมตร

ควรจำไว้ว่า Intel นั้นแข็งแกร่งด้วย SuperFin 10 นาโนเมตร นั่นคือ AMD ต้องเปิดตัว Zen 3 และ RDNA 2 ใน 7 นาโนเมตรโดยไม่มี + และ EUV อาจเป็นโซลูชันชั่วคราวใน 7 นาโนเมตรหากในที่สุดพวกเขาก็ข้ามประสิทธิภาพสูง 5 นาโนเมตร

และไม่ใช่ว่าทุกอย่างจะมีความหนาแน่นอย่างที่เราเห็นการออกแบบของเซลล์ความสูงประตูและจำนวนการเชื่อมต่อที่ไม่มีที่สิ้นสุดมีความสำคัญหรือมากกว่าแค่การได้รับทรานซิสเตอร์ต่อตารางมิลลิเมตร