ความสนใจล่าสุดจากทั้ง Google และ เอเอ็มดี ในเทคโนโลยี SoiC ของ TSMC ได้จุดประกายความอยากรู้อยากเห็นเกี่ยวกับสิ่งที่เราจะได้เห็นในอนาคตโดยใช้วิธีใหม่ในการสร้างวงจรรวม เทคโนโลยี SoIC ของ TSMC ซ่อนความลับอะไรไว้? เราจะได้เห็นมันถูกนำมาใช้ในพีซีของเราหรือเป็นสิ่งที่อยู่ไกลเกินเอื้อม?

หนึ่งในแนวรบที่ได้รับการตรวจสอบมากขึ้นในช่วงไม่กี่ปีที่ผ่านมาคือการพัฒนาระบบบรรจุภัณฑ์ที่ก้าวไปไกลกว่ารุ่นทั่วไปโดยใช้ชิปเสาหิน ตัวอย่างล่าสุดคือ SoIC ของ TSMC ซึ่งดึงดูดความสนใจของ Google และ AMD แยกกัน

TSMC SoIC packaging คืออะไร?

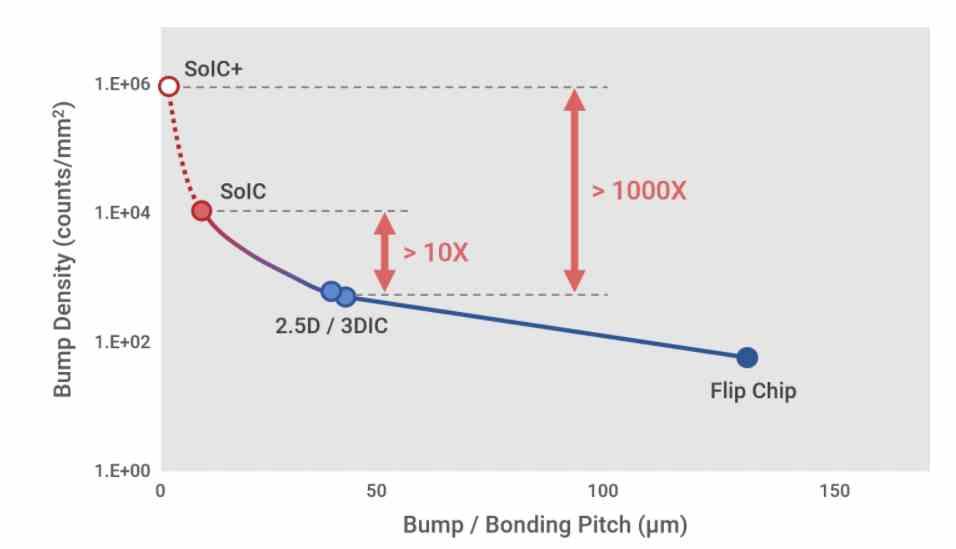

ในความเป็นจริง, SoiC ไม่มีอะไรมากไปกว่าการเชื่อมต่อโครงข่ายที่เชื่อมต่อชิปสองตัวของวงจรรวมสามมิติ โดยที่แนวคิดของ TSMC คือการเพิ่มจำนวนการเชื่อมต่อนอกเหนือจากที่ใช้ในการออกแบบประเภทนี้ในรูปแบบทั่วไป

เหตุผล? การเพิ่มจำนวนการเชื่อมต่อหมายความว่าต้องใช้ความเร็วสัญญาณนาฬิกาน้อยลงเพื่อให้ได้ความเร็วสัญญาณนาฬิกาที่กำหนดซึ่งแปลเป็นการใช้พลังงานที่ต่ำกว่ามากต่อบิตของข้อมูลที่ส่ง

เพื่อให้เข้าใจสิ่งนี้เราต้องจำไว้ว่าการเพิ่มความเร็วสัญญาณนาฬิกาเป็นสองเท่าของอินเทอร์เฟซนั้นใช้พลังงานถึงสี่เท่าดังนั้นจึงเป็นสิ่งสำคัญอย่างยิ่งที่จะสามารถสร้างอินเทอร์เฟซการสื่อสารด้วยพินจำนวนมากได้

ชิป 3DIC คืออะไร?

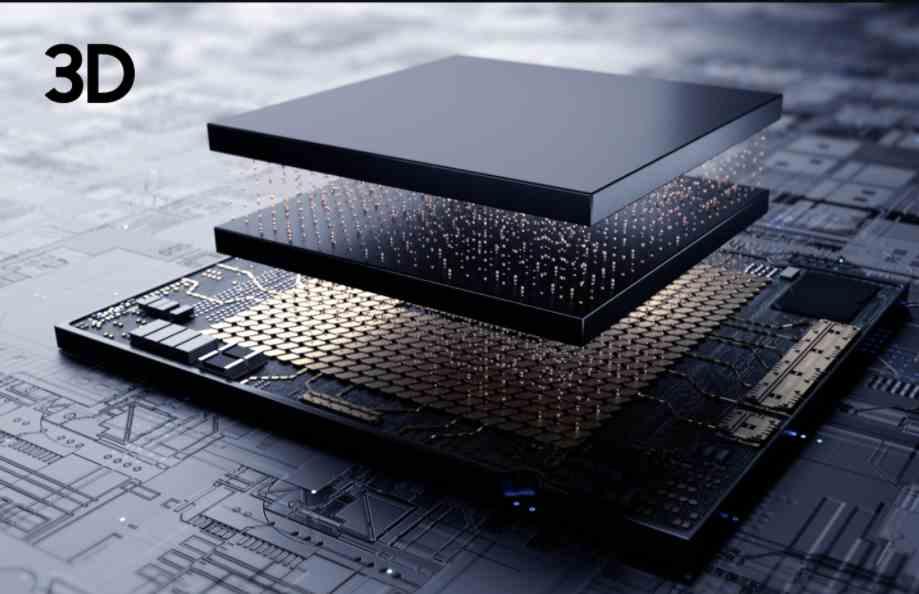

3DIC เรียกว่า 3DIC สำหรับวงจรรวมเหล่านั้นซึ่งประกอบด้วยชิปหลายตัว แต่ไม่พบในระดับเดียวกัน แต่อยู่ในหลาย ๆ ตัวดังนั้นแทนที่จะติดตั้งบนชิปเสาหินขนาดใหญ่ในแนวนอนจะติดตั้งบนชิปขนาดเล็กหลายตัวในแนวตั้งเพื่อใช้งาน สำหรับการเชื่อมต่อของจุดเชื่อมต่อที่ผ่านซิลิคอนของโปรเซสเซอร์

สิ่งนี้มีข้อดีหลายประการประการแรก สามารถสร้างชิ้นเล็ก ๆ และเข้าถึงชิปจำนวนมากต่อเวเฟอร์ . ประการที่สอง การเชื่อมต่อแนวตั้งจะเพิ่มจำนวนการเชื่อมต่อที่เป็นไปได้ ซึ่งช่วยให้เราสามารถลดความเร็วสัญญาณนาฬิกาสำหรับแต่ละพินได้อย่างสมบูรณ์และทำให้การใช้พลังงานลดลงมาก

จนถึงตอนนี้เราได้เห็นโครงสร้าง 3DIC ที่ใช้หน่วยความจำทั้งในความทรงจำเช่น HBM และหน่วยความจำ 3D NAND แต่ขั้นตอนต่อไปคือการรวมลอจิกและหน่วยความจำในการกำหนดค่า 3DIC หรือรวมตรรกะหลาย ๆ ส่วนเข้าด้วยกัน

ความท้าทายในปัจจุบันไม่ได้อยู่ที่ความเร็วในการคำนวณ แต่อยู่ที่การถ่ายโอนข้อมูล

ปัญหาอย่างหนึ่งที่วิศวกรเผชิญในปัจจุบันเมื่อออกแบบระบบใหม่ไม่ใช่จำนวนการดำเนินการต่อรอบและ / หรือคำแนะนำที่การออกแบบสามารถบรรลุได้ แต่ การออกแบบมีการขนส่งข้อมูลเพียงพอที่จะทำงานในอัตราส่วนการใช้พลังงานคงที่หรือไม่

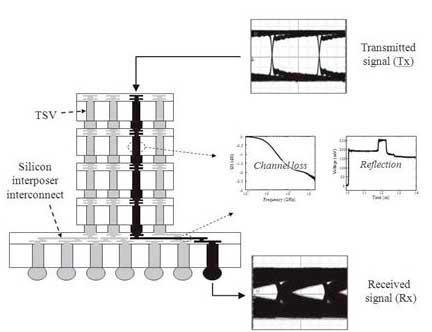

การพัฒนาเทคโนโลยีบนพื้นฐานของการสื่อสารผ่านทางซิลิคอน TSV เริ่มขึ้นเมื่อทศวรรษที่แล้วและวัตถุประสงค์หลักคือการเพิ่มแบนด์วิดท์ปริมาณข้อมูลที่ส่งไปเสมอในขณะที่ยังคงการใช้พลังงานโดยเฉลี่ย

วิธีเดียวที่จะสามารถสร้างโปรเซสเซอร์ที่ใช้ชิปเล็ตได้ ไม่ว่าจะในการกำหนดค่า 3DIC หรือ 2DIC ที่กระจัดกระจายอยู่ในตัวแทรกสอดก็ต้องแน่ใจว่า สร้างอินเทอร์เฟซการสื่อสารที่ตอบสนองความต้องการด้านพลังงานเหล่านั้น และวิวัฒนาการที่ง่ายที่สุดคือการเพิ่มจำนวนอินเทอร์เฟซเพื่อให้สามารถลดการใช้พลังงานสำหรับแบนด์วิดท์ที่กำหนดได้

วิธีเดียวที่จะสามารถสร้างโปรเซสเซอร์ที่ใช้ชิปเล็ตได้ ไม่ว่าจะในการกำหนดค่า 3DIC หรือ 2DIC ที่กระจัดกระจายอยู่ในตัวแทรกสอดก็ต้องแน่ใจว่า สร้างอินเทอร์เฟซการสื่อสารที่ตอบสนองความต้องการด้านพลังงานเหล่านั้น และวิวัฒนาการที่ง่ายที่สุดคือการเพิ่มจำนวนอินเทอร์เฟซเพื่อให้สามารถลดการใช้พลังงานสำหรับแบนด์วิดท์ที่กำหนดได้

เมื่อเราพูดถึงการส่งข้อมูล เราไม่ได้หมายถึงการสื่อสารกับหน่วยความจำภายนอกเท่านั้น แต่ในกรณีของการแบ่งชิปออกเป็นชิพเล็ตต่างๆก็ต้องมั่นใจว่า การใช้พลังงานของสายไฟไม่พุ่งสูงขึ้นเมื่อส่งสัญญาณ ปริมาณข้อมูลเดียวกัน เนื่องจากสิ่งที่คู่กันคือเส้นทางการสื่อสารมีความยาวมากขึ้นทำให้การใช้พลังงานเพิ่มขึ้นอย่างมาก

ประเภทบรรจุภัณฑ์ SoiC

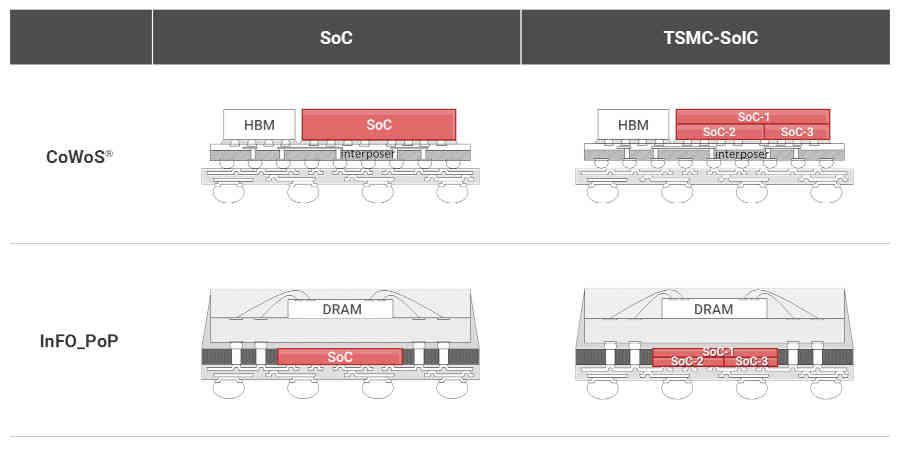

ในตอนแรกเรามีไฟล์ การกำหนดค่า CoWoS ซึ่งโดยปกติจะเป็นการกำหนดค่า 2..5DIC ซึ่งตั้งชื่อตามความจริงที่ว่าพวกเขามักจะรวมชิปเสาหินที่เชื่อมต่อกับตัวแทรกซึ่งทำหน้าที่เป็นเส้นทางเพื่อเข้าถึงหน่วยความจำ 3DIC ตามปกติ HBM

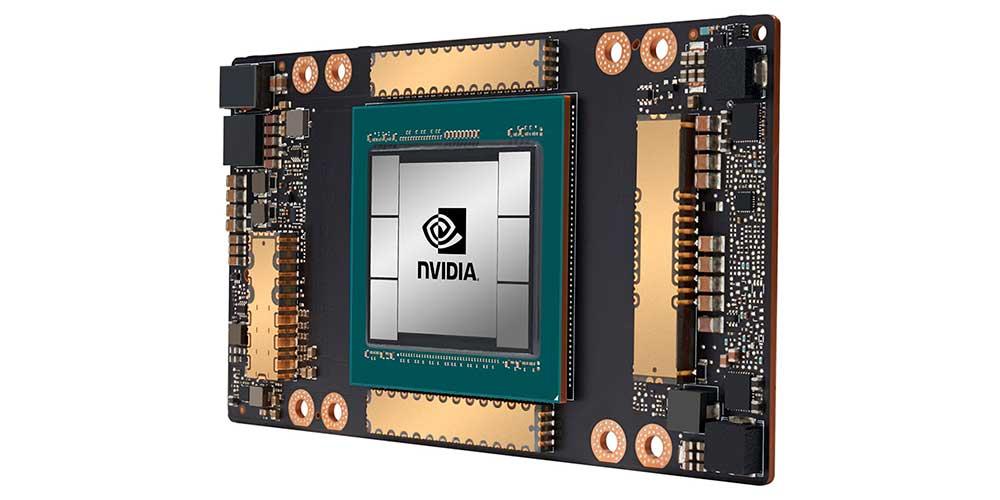

การกำหนดค่าประเภทนี้ไม่ประสบความสำเร็จอย่างมากในตลาดในประเทศเนื่องจากต้นทุนการผลิตที่สูง แต่ใช้ในรูปแบบ คอมพิวเตอร์สมรรถนะสูง ตลาดซึ่ง AMD CDNA ที่เพิ่งเปิดตัวใช้การกำหนดค่านี้รวมถึงไฟล์ NVIDIA A100 และการตั้งค่าหน่วยประมวลผล Tensor ของ Google

อันดับที่สองเรามีไฟล์ ข้อมูล-POP แพคเกจและกับพวกเขาเราจะไม่ไปสุดขั้วอื่น ๆ เนื่องจากเป็นการกำหนดค่า ที่ใช้ในตลาดสำหรับสมาร์ทโฟนและอุปกรณ์ PostPC อื่น ๆ ความจริงของการพูดถึง SoC สำหรับสมาร์ทโฟนที่เป็น 3DIC จริงๆประกอบด้วยชิปหลายตัวเปิดประตูสู่การปรับแต่งที่แปลกประหลาดและวิธีใหม่ในการใช้ประโยชน์จากพื้นที่ จำกัด ของ SoC สำหรับอุปกรณ์ Post-PC

ไม่ว่าจะเป็นบรรจุภัณฑ์ประเภทใดสิ่งที่ TSMC พยายามแสดงให้เราเห็นก็คือสามารถแปลง SoC เสาหินให้เป็น 3DIC ที่ใช้การเชื่อมต่อระหว่างกันของ SoIC แม้ว่า TSMC จะไม่ได้พูดถึงมันก็เปิดโอกาสให้ CPU และ GPU ในซ็อกเก็ตและรูปแบบทั่วไป ปัจจัยที่ใช้เทคโนโลยี SoIC แต่นี่คือสิ่งที่ TSMC ยังไม่ได้ประกาศแม้ว่าจะมีความเป็นไปได้