แม้ว่า PCIe 4.0 จะมาพร้อมกับเราและไม่ถึงกับ NVIDIA เป็นรุ่นล่าสุดด้วยกราฟิกการเล่นเกมมันเกิดขึ้นเช่นกันที่สามแบรนด์ชั้นนำในตลาดเดสก์ท็อปและเซิร์ฟเวอร์รวมถึง HPC กำลังรอคอยตัวต่อไป PCIe 5.0 รีลีส ตามที่อาจ ทำไมความเร็วมากในการต้องการใช้มัน? เหตุผลใดผลักดันให้ทั้งสามต้องการรวมคุณสมบัติของพวกเขา

มีความจำเป็นที่จะต้องคำนึงถึงในตอนแรกและเพื่อทำความเข้าใจกับข้อกำหนดของกันและกันว่า PCIe 5.0 นั้นเป็นก้าวกระโดดที่สำคัญมากเมื่อเทียบกับรุ่นก่อนและใหญ่ทั้งสามมีตาอยู่เหนือการเล่นเกม

![]()

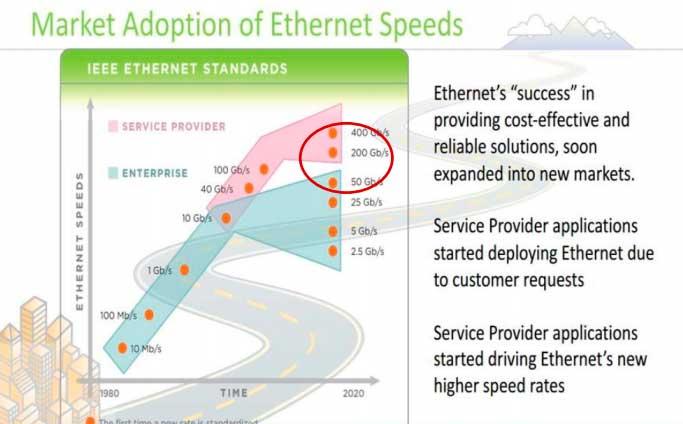

โซลูชันเครือข่ายระดับสูงด้วย 400 Gb Ethernet หรือ dual 200 Gb / s InfinityBand ตัวเร่งความเร็วและ GPU แต่เหนือสิ่งอื่นใดที่สามารถใช้งานได้อย่างต่อเนื่อง สารตั้งต้น L1 สำหรับการใช้พลังงานที่ต่ำกว่านั้นเป็นการปรับปรุงที่รออยู่ แต่สำหรับสิ่งนี้เราต้องเข้าใจการปรับปรุงที่รถใหม่คันนี้จะนำมาให้

PCIe 5.0: ข่าวสารและฟีเจอร์

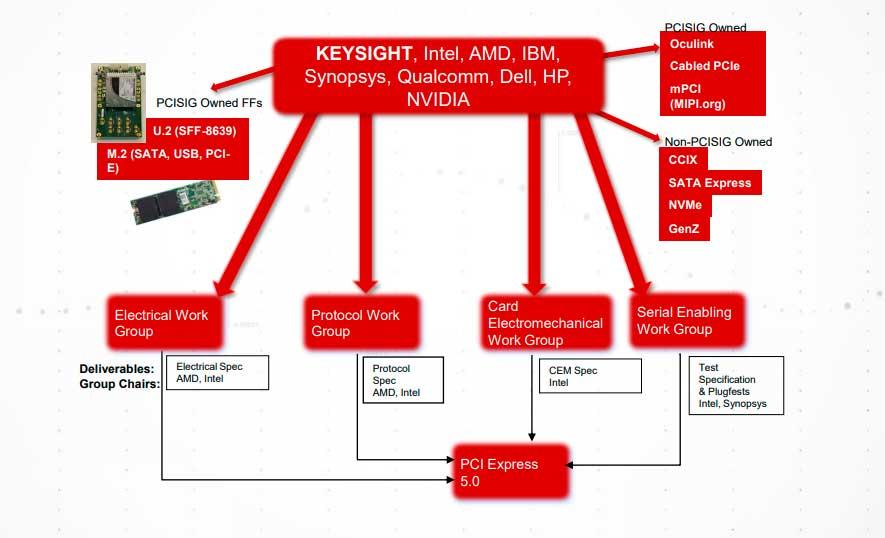

หากเราดูโรดแมพเดิมสำหรับมาตรฐานนี้เราจะเห็นว่าอย่างน้อยที่สุดมันจะถูกเปิดตัวในอีกสองปีข้างหน้าโดยที่ PCIe 5.0 จะลากไปทางด้านหลังของเวอร์ชั่น 4.0 รุ่นก่อน โดยหลักการแล้วจะถึงจุดหนึ่งในปี 2021 โดยที่ PCISIG สั่งให้มีการแก้ไขร่างครั้งแรกเมื่อปลายปี 2019 ซึ่งเป็นที่ตั้งของมาตรฐานดังกล่าว

นวนิยายหลักของรุ่นนี้และสิ่งที่คาดหวังคือ:

- ปรับปรุงตัวเชื่อมต่อ SMT

- ข้อผิดพลาดเช่นเดียวกับรุ่นก่อนหน้า

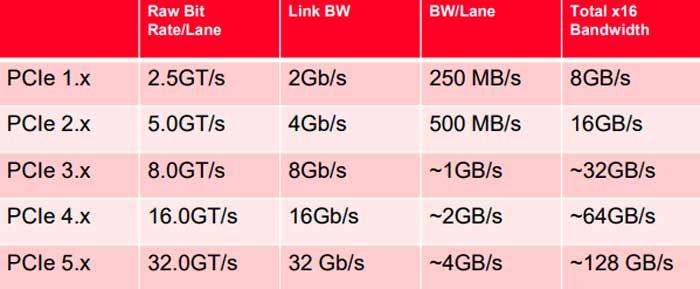

- ส่งสัญญาณซ้ำได้ถึง 32 GT / s

- คุณต้องเปิดใช้งานการลดความเร็วเพื่อให้เป็นไปตามข้อกำหนดเท่านั้น

- EIEOS

- การปรับปรุงบิตข้อมูลอัตรา

- การเข้ารหัสถาวร 128/130

- ขาดทุนสะสมระหว่าง 35 และ 36 เดซิเบล

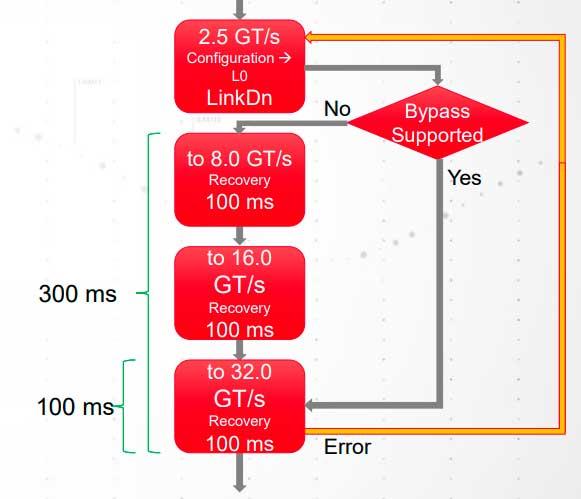

- การทำให้เท่าเทียมกัน 8 GT -> 16 GT -> 32 GT / s

- สเกลควบคุมการไหล

นอกจากนี้เราไม่สามารถลืมความเข้ากันได้ย้อนยุคกับ PCIe รุ่นก่อนหน้าทั้งหมด แต่ถ้าเรามุ่งเน้นไปที่เครือข่ายและ FPGAs การปรับปรุงจะไม่สิ้นสุดที่นั่น:

- เบอร์ 10e-12

- TX ค่าที่ตั้งล่วงหน้า P0-P10

- วิธีการเดียวกันสำหรับ TX และ RX ใน Gen 4

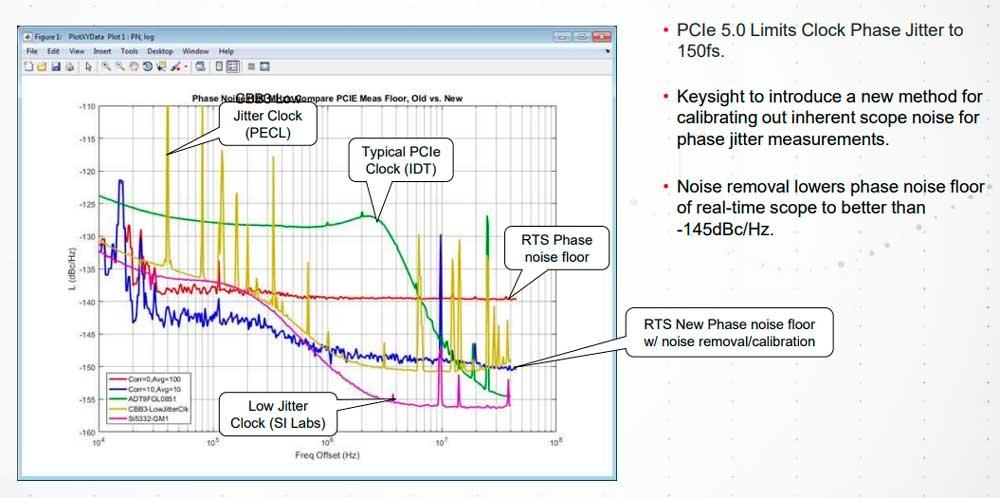

- พารามิเตอร์แรงดันไฟฟ้า TX และ jitter เหมือนกับ Gen4

โทโพโลยีของแต่ละช่องทางสำคัญในการนำไปใช้และความเร็ว

สิ่งแรกที่เราต้องเข้าใจคือปัจจุบันทุก บริษัท ต้องการและในอนาคตอันใกล้คือความเร็ว มันเป็นข้อเรียกร้องหลักของ PCIe 5.0 แต่สำหรับสิ่งนี้พวกเขาทั้งหมดจะต้องปรับให้เข้ากับเกณฑ์บางอย่างในโทโพโลยีที่จะกำหนดความต้องการมากขึ้นในแต่ละช่อง

ดังนั้น PCIe 5.0 จะระบุแชนเนลที่สั้นกว่าด้วย a โอห์ม 50 การสิ้นสุดสำหรับการวัดค่ากระวนกระวายใจซึ่งนอกจากนี้ขีด จำกัด ล่างของแบนด์วิดท์ PLL ถูกตั้งค่าเป็นเพียง 0.5 MHz สำหรับ 16 GT / s

สิ่งนี้มีความสำคัญสำหรับระบบ AI และ ML ซึ่งประมวลผลข้อมูลจำนวนมากและดังที่เราทราบตลาดกำลังขยายตัวอย่างฉับพลันในช่วงไม่กี่ปีที่ผ่านมาและไม่มีอะไรบ่งบอกว่ามันจะไม่ดำเนินต่อไปในลักษณะนี้ ด้วยอัตราการรับส่งข้อมูลรายวันประมาณ 4TB นั้นเป็นที่เข้าใจได้ว่าจำเป็นต้องใช้แบนด์วิดท์ที่มากขึ้น

หากเราเพิ่มการใช้งานนี้ CXL หรือ CCXI เป็นวิธีการเชื่อมต่อโครงข่ายใหม่ระหว่างอุปกรณ์เชื่อมโยงกันเราสามารถทราบว่าตลาดอยู่ที่ไหนและอนาคตของอุตสาหกรรมจะเป็นอย่างไร สำหรับเดสก์ท็อปนั้นทั้งสามมีขนาดใหญ่กว่าในแง่ของความเร็วกับ PCIe 4.0

Ampere G100 ไม่ได้คาดหวังว่าจะสามารถเติมแบนด์วิดท์ได้อย่างสมบูรณ์ดังนั้นกราฟิกเกมมีแนวโน้มที่จะดำเนินต่อไปใน Gen4 ต่อไปอีกไม่กี่ปี