การแนะนำล่าสุดและการเปิดตัว เอเอ็มดี โปรเซสเซอร์ Ryzen 5000 ซีรีส์ซึ่งใช้สถาปัตยกรรม Zen 3 มาพร้อมกับมงกุฎสำหรับ AMD อย่างน้อยก็ในช่วงเวลาหนึ่งเมื่อมีอำนาจ แต่อะไรล่ะที่ทำให้สถาปัตยกรรม Zen 3 เร็วขนาดนี้? คุณได้เพิ่มองค์ประกอบใดบ้างในสถาปัตยกรรม Zen รุ่นที่สามเพื่อประสิทธิภาพที่ดีขึ้น

ก่อนเริ่มต้นควรสังเกตว่า Ryzen 5000 ไม่ใช่ผู้สืบทอดโดยตรงของ AMD Ryzen 4000 ซึ่งเป็น SoC แบบเสาหิน แต่แทนที่จะเป็น Ryzen 3000 ตั้งแต่นั้นมา Ryzen 5000 ยังเป็นระบบ MCM ขึ้นอยู่กับ chiplets

ในระบบนี้เรามีอยู่ในมือข้างหนึ่ง IOD ที่ Northbridge ของระบบ ตั้งอยู่ , รับบัพติศมาเป็น Scalable Data Fabric หรือ SDF โดย AMD และ Southbridge ที่เรียกว่า IO Hub โดย บริษัท ของ Ryzens และราเดียนส์ กล่าวว่า IOD ไม่ได้เปลี่ยนแปลงในส่วนที่เกี่ยวกับ Ryzen 3000 ยกเว้นในความเป็นจริงในการรองรับความทรงจำที่เร็วขึ้นเนื่องจากผ่าน IOD ที่คอร์สามารถเข้าถึงได้ แรม ของระบบ

อย่างไรก็ตามเราไม่สามารถพูดได้ว่าพวกเขาใช้ IO Die ของ Ryzen 3000 ตามที่เป็นอยู่และทำการปลูกถ่ายตามที่เป็นอยู่ แต่พวกเขาได้ปรับปรุงมันผ่านประสบการณ์ของพวกเขาเมื่อสร้าง Ryzen 4000 สำหรับคอมพิวเตอร์ที่มีการบริโภคต่ำกว่าเดสก์ท็อปพีซี

มีที่ไหนบ้าง การเปลี่ยนแปลงที่สำคัญมากอยู่ใน CCD หรือ Core Complex Die ชิปขนาดเล็กที่เก็บแกนต่างๆและลำดับชั้นแคชซึ่งเป็นจุดที่มีการเปลี่ยนแปลงที่สำคัญที่สุด

สถาปัตยกรรม Core Complex Die of Zen 3 ใหม่

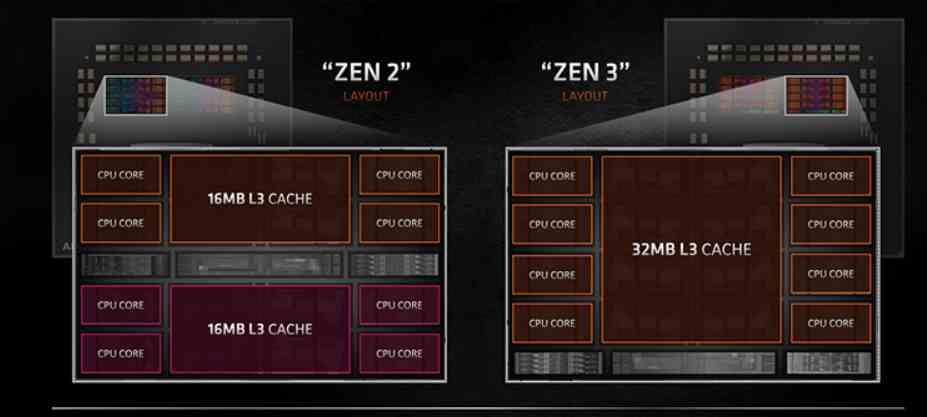

พื้นที่ CCD ใน Zen 2 ถูกสร้างขึ้น CCX สองชุด มี 4 คอร์แต่ละคอร์ด้วย L3 cache ที่ใช้ร่วมกันภายใน CCX แต่ละตัว . ซึ่งทำให้เกิดปัญหาเวลาแฝงเมื่อหลายคอร์ภายใน CCD เดียวกัน แต่ใน CCX ต่างกันต้องสื่อสารกันเนื่องจากถ้านิวเคลียสต้องสื่อสารกับตัวอื่นที่อยู่ใน CCX อื่นก็ต้องผ่าน IOD แม้ว่าจะอยู่บน CCD เดียวกัน

การเปลี่ยนแปลงที่ AMD ทำในสถาปัตยกรรม Zen 3 นั้นง่ายมากพวกเขาทำให้ 8 คอร์แชร์ L3 cache แทนที่จะเป็น 4 แกนในเวลาเดียวกัน . ดังนั้นเราจึงเปลี่ยนจากการมี CCX 2 คอร์ 4 ตัวต่อ CCD ถึง 1 8-core CCX ต่อ CCD . สิ่งนี้ในแอปพลิเคชันที่มีจุดมุ่งหมายเพื่อทำงานโดยมีแกน 8 หรือน้อยกว่าส่งผลให้ได้เปรียบด้านประสิทธิภาพ

แต่ที่อ MD ได้ทำการปรับปรุง ที่ระดับของแต่ละคอร์จะอยู่ใน โหลด / จัดเก็บหน่วย เช่นเดียวกับใน ส่วนหน้าหรือชุดควบคุม , การปรับปรุงที่เป็นกุญแจสำคัญในการบรรลุประสิทธิภาพเฉลี่ย 19% จากรุ่นก่อน, Zen 2

ที่สำคัญคือชุดควบคุม

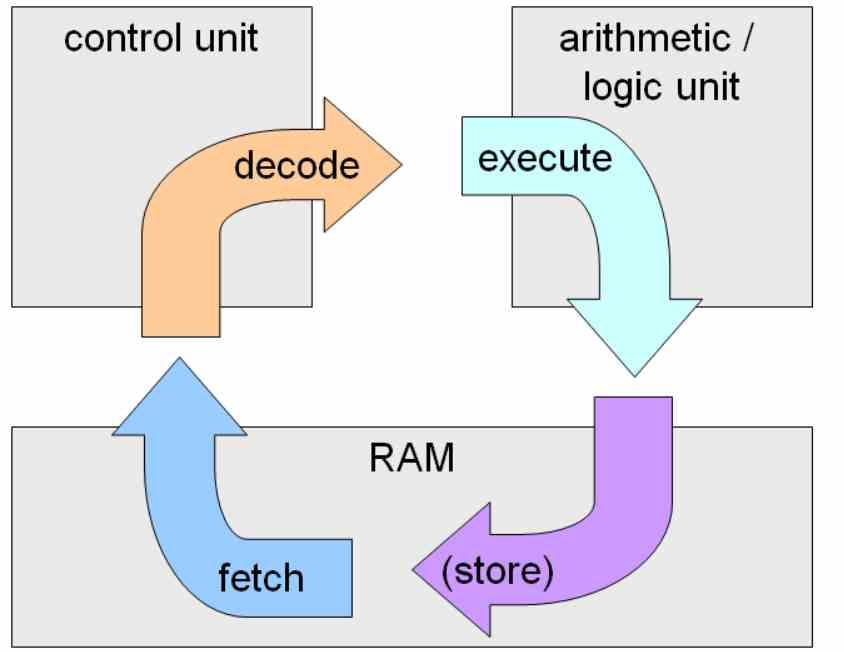

เมื่อเราพูดถึง ส่วนหน้าเราหมายถึงชุดควบคุมของไฟล์ ซีพียูในขณะที่ ALU เป็น Back-end ภายใน วงจรการเรียนการสอน , ดึง - ถอดรหัส - ดำเนินการ, สองขั้นตอนแรกคือการทำงานของชุดควบคุม ในขณะที่ส่วนที่สองคือการทำงานของ ALU หรือหน่วยปฏิบัติการ

ทั้งหมด ร่วมสมัย x86 โปรเซสเซอร์ไม่ได้ ดำเนินการตามคำแนะนำภายใต้ ISA ดังกล่าว แต่แทน ถอดรหัสคำแนะนำใน ISA RISC ภายใน นั่นคือที่ที่คำสั่งถูกดำเนินการจริงในหน่วยการดำเนินการ ISA ภายในนี้สามารถเปลี่ยนแปลงได้แม้กระทั่งระหว่างสมาชิกของสถาปัตยกรรมเดียวกันและเป็นกุญแจสำคัญเมื่อเพิ่ม IPC ของโปรเซสเซอร์

นั่นคือเหตุผล AMD ได้ทำการปรับปรุงชุดควบคุมใหม่ และนำไฟล์ ISA ภายในใหม่ที่มีประสิทธิภาพมากขึ้น ที่ช่วยให้คำสั่งดำเนินการในรอบนาฬิกาต่อคำสั่ง (CPI) น้อยลงทำให้จำนวนคำสั่งเฉลี่ยต่อรอบเพิ่มขึ้นด้วย .