เป็นไปได้มากว่าคุณมีอุปกรณ์อิเล็กทรอนิกส์ที่ใช้ เทคโนโลยี FinFET และคุณไม่รู้ เทคโนโลยีนี้มีอยู่ใน SSD และโปรเซสเซอร์รวมถึงส่วนประกอบอื่น ๆ ดังนั้นเราขอให้คุณเข้าร่วมกับเราเพื่อค้นพบมัน

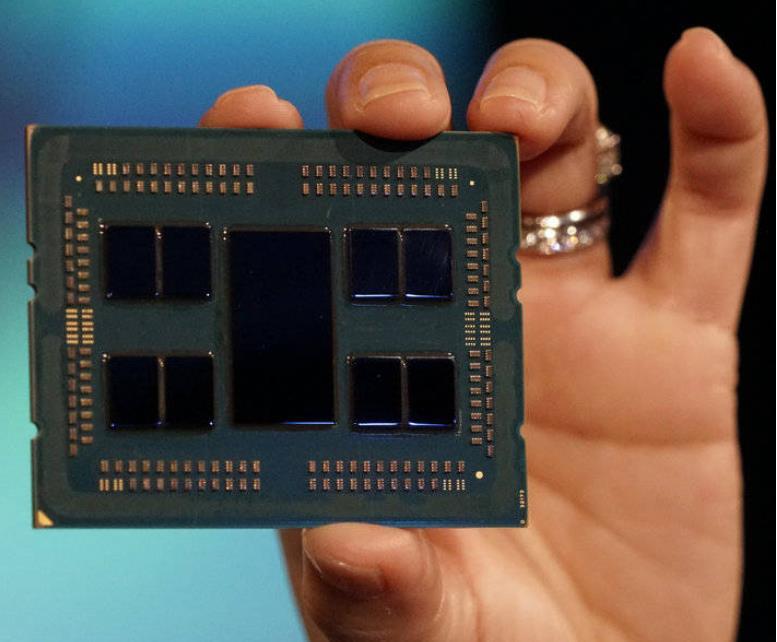

อินเทล เป็นหนึ่งในผู้ผลิตรายแรกที่ใช้เทคโนโลยีทรานซิสเตอร์ FinFET ในการผลิตโปรเซสเซอร์ ทรานซิสเตอร์ FinFET มีอยู่ในอุปกรณ์อิเล็กทรอนิกส์ส่วนใหญ่ แต่ทุกคนไม่ทราบแน่ชัดว่าเทคโนโลยีนี้คืออะไรหรือใช้ที่ไหน

เทคโนโลยีการผลิต FinFET คืออะไร?

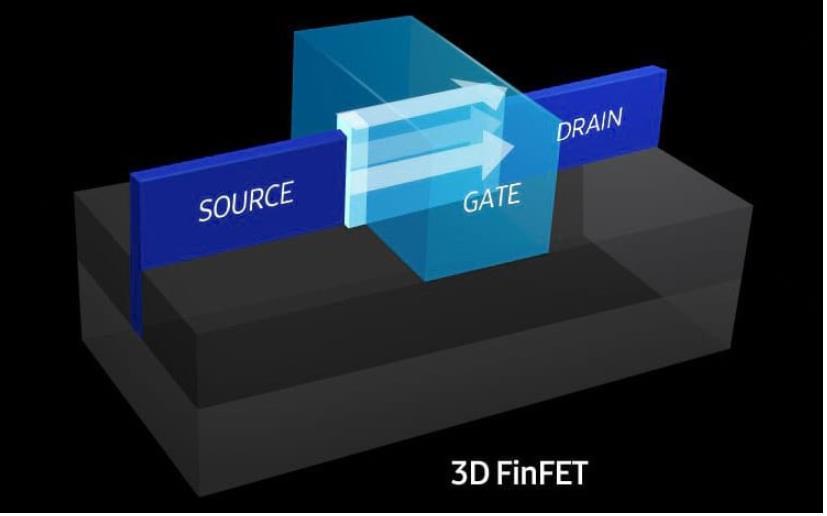

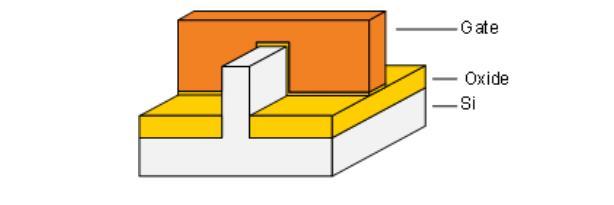

คำว่า FinFET เป็นคำย่อของ " Fin Field Effect ทรานซิสเตอร์ “ ซึ่งแปลเป็นภาษาสเปนหมายถึง“ ทรานซิสเตอร์เอฟเฟกต์สนามครีบ (ครีบ)” เป็นทรานซิสเตอร์ที่สร้างขึ้นบนพื้นผิวฉนวนซิลิโคน (SOI) ทรานซิสเตอร์ FinFET ประกอบด้วยแหล่งที่มาหน้าสัมผัสท่อระบายน้ำและประตูเพื่อควบคุมการไหลของกระแสไฟฟ้า มันแตกต่างจาก MOSFETs ในการรวมแท่ง 3D ที่ด้านบนของพื้นผิวซิลิกอน: ครีบ

อินเทล เป็นคนแรกที่ใช้เทคโนโลยี FinFET ใน 2012 กับของตน สะพานไม้เลื้อย โปรเซสเซอร์ FinFET เป็นโครงสร้าง 3 มิติที่ซ้อนกันอยู่ด้านบนของวัสดุพิมพ์ การสร้างทรานซิสเตอร์ FinFET ประกอบด้วยขั้นตอนต่อไปนี้:

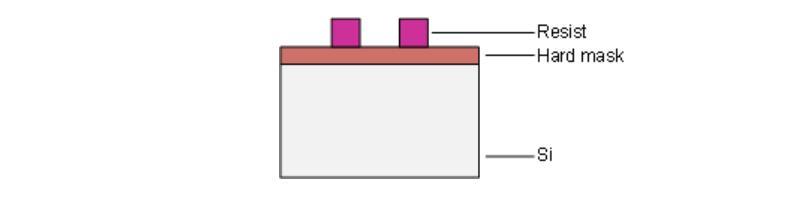

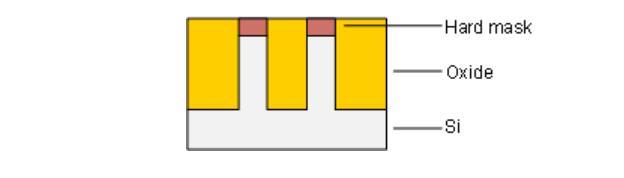

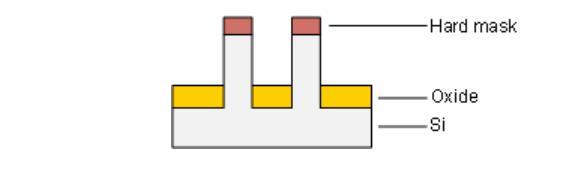

- พื้นผิว . เป็นฐานของทรานซิสเตอร์ FinFET ทุกตัวและมีชั้นแข็งอยู่ด้านบน

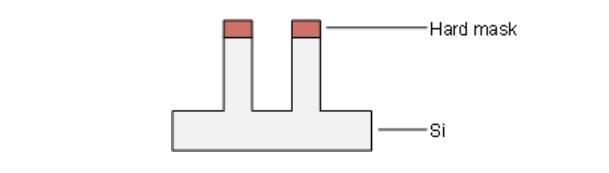

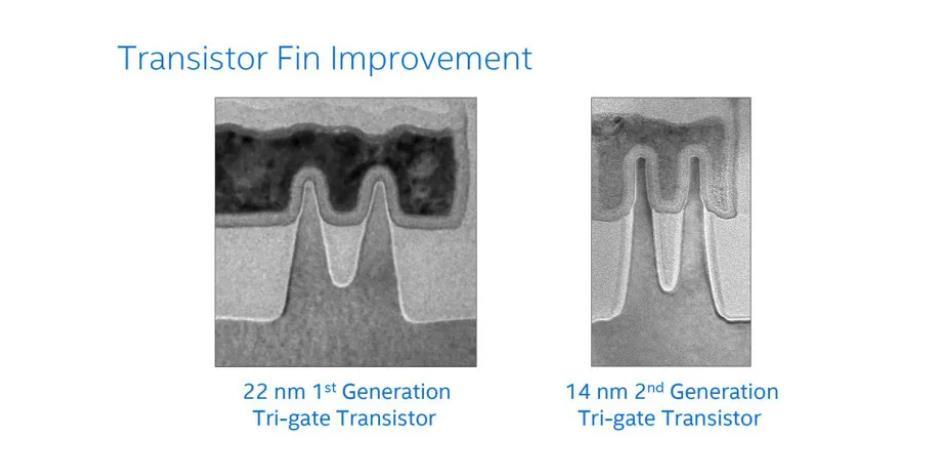

- ครีบ ปัญหาที่สำคัญคือขนาดของครีบ ตัวอย่างเช่นในกระบวนการ 22 นาโนเมตรความกว้างของครีบอาจเป็น 10-15 นาโนเมตร

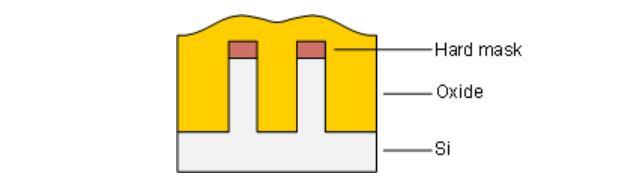

- การสะสมของสนิม . ด้วยการสะสมจุดมุ่งหมายคือการแยก aletras ออกจากกัน

- planarization . มีบางครั้งที่สนิมแผ่ออกและหน้ากากแข็งทำหน้าที่เป็นชั้นเอง

- แกะสลักกลวง . จำเป็นต้องใช้กระบวนการแกะสลักอื่นเพื่อลดฟิล์มออกไซด์และทำให้เกิดฉนวนด้านข้างของครีบ

- การติดตั้งประตู . ชั้นของโพลีซิลิคอนวางอยู่บนครีบและมากถึง 3 ประตูถูกพันรอบช่อง

ทรานซิสเตอร์แต่ละตัวมีครีบสองอันและประตูควบคุมสองอัน ที่นี่ช่องทางการไหลมีการควบคุมมากมาย แต่ ปัญหาของมันคือพื้นที่ : ถ้าประตูลดลงพื้นที่ในการเพิ่มครีบจะน้อยลง ครีบเหล่านี้ประกอบไปด้วยแหล่งกำเนิดและท่อระบายน้ำเพื่อให้มีปริมาณมากขึ้นในพื้นที่เมื่อเทียบกับทรานซิสเตอร์แบบแบนแบบเดิม

ปัญหาเกิดขึ้นเมื่อเราต้องการไฟล์ กระบวนการพิมพ์หินขนาดเล็ก วัตถุประสงค์ที่ดำเนินการโดย เอเอ็มดี เพื่อให้ได้ประสิทธิภาพที่มากขึ้นและมีประสิทธิภาพมากขึ้น การทำลิโธกราฟีกำหนดจำนวนทรานซิสเตอร์ที่เข้าไปในตารางมิลลิเมตร ในตอนท้ายของวันทรานซิสเตอร์จะเปิดและปิด แต่เพื่อให้บรรลุสิ่งนี้จะมีขนาดในประตูที่อนุญาตให้เปิดหรือตัดกระแสไฟฟ้าผ่าน

ความยาวของประตูเป็นกุญแจสำคัญของทรานซิสเตอร์นี้: ยิ่งความยาวสั้นลงความแม่นยำในการควบคุมกระแสก็จะยิ่งมากขึ้นและทรานซิสเตอร์ต่อตารางเมตรก็ยิ่งมากขึ้นเท่านั้น อย่างไรก็ตามไม่ควรใช้ในทางที่ผิดเนื่องจากประสิทธิภาพอาจได้รับผลกระทบ

ดังนั้นขั้นตอนการสัมผัสของทรานซิสเตอร์ ( ระยะห่างเพื่อหดตัว ) มาถึงโซลูชันที่ผู้ผลิตคิดค้นขึ้นเพื่อปรับปรุงทรานซิสเตอร์ Intel ดำเนินการแก้ปัญหานี้ด้วยโปรเซสเซอร์รุ่นล่าสุดซึ่งส่งผลให้มีชื่อเสียง 14 นาโนเมตร ++ กระบวนการ. ตาม TSMC ความยาวขั้นต่ำคือ 25 นาโนเมตร: ถ้าเราลดตัวเลขนั้นประสิทธิภาพของทรานซิสเตอร์จะแย่ลง

เทคโนโลยี FinFET ขึ้นอยู่กับ กฎของมัวร์ ซึ่งช่วยให้ผู้ผลิตเซมิคอนดักเตอร์สามารถสร้างโปรเซสเซอร์และโมดูลหน่วยความจำขนาดเล็กได้โดยมีประสิทธิภาพที่ดีขึ้นและใช้พลังงานน้อยลง เป็นเทคโนโลยีที่ใช้เป็นหลักในการผลิตโปรเซสเซอร์ แรม ความทรงจำและฮาร์ดไดรฟ์ SSD

อนาคตไม่ได้จับมือกับ FinFET

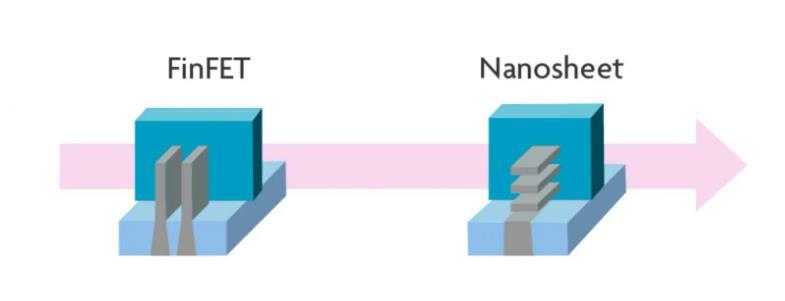

โปรดทราบว่าทุกอย่างกำลังก้าวหน้าและเทคโนโลยี FinFET เริ่มล้าสมัยเนื่องจากมีข้อ จำกัด บางประการ ดังนั้น แผ่นนาโน ปรากฏขึ้นเทคโนโลยีที่ทรานซิสเตอร์มีอยู่ ครีบซ้อนกันในแนวตั้ง แทนที่จะเป็นแนวนอน ดังนั้นจึงเรียกว่า "แผ่นนาโน" ซึ่งบัญญัติขึ้นโดยการจัดเรียงคล้ายกับแผ่นงานของหนังสือ

ทรานซิสเตอร์นี้จะมี ชั้นของซิลิกอน และ Sige จัดเรียงในแนวตั้งและจะเป็นประตูสำหรับการกำหนดมาตรฐานของกระบวนการ 5 นาโนเมตร เช่นเดียวกับเทคโนโลยีใหม่ ๆ มีอุปสรรคเริ่มต้น: การออกแบบมีความซับซ้อนต้องใช้ตัวเว้นระยะภายในเพื่อควบคุมแรงดันไฟฟ้าและท่อระบายน้ำ

เทคโนโลยีทรานซิสเตอร์นี้อาจยังคงเป็นเรื่องเล็ก ๆ น้อย ๆ ซึ่งเป็นสิ่งที่ดีกว่าที่จะเกิดขึ้น ในทำนองเดียวกันการซ้อนในแนวตั้งก็เป็นวิธีที่เราเห็นในไฟล์ หน่วยความจำ HBM2e .