แนวคิดของ Cache DRAM ประกอบด้วยการเพิ่มระดับแคชเพิ่มเติมระหว่างโปรเซสเซอร์และ แรม หน่วยความจำเพื่อเพิ่มประสิทธิภาพของอดีต แต่การเปลี่ยนแปลงในสถาปัตยกรรมของโปรเซสเซอร์มีความหมายอย่างไรและแนวคิดนี้ทำงานอย่างไร? เราอธิบายให้คุณทราบและโดยบังเอิญว่าโปรเซสเซอร์ใดจะใช้สถาปัตยกรรมนี้

ไม่กี่วันที่ผ่านมา Apple สิทธิบัตรปรากฏขึ้นซึ่งมีการกล่าวถึงการใช้ Cache DRAM ในโปรเซสเซอร์ในอนาคตซึ่งเป็นแนวคิดที่แม้ว่ามันอาจจะดูแปลกใหม่ แต่เราจะทำให้เข้าใจผิด

หน่วยความจำ DRAM เป็นแคชความขัดแย้ง

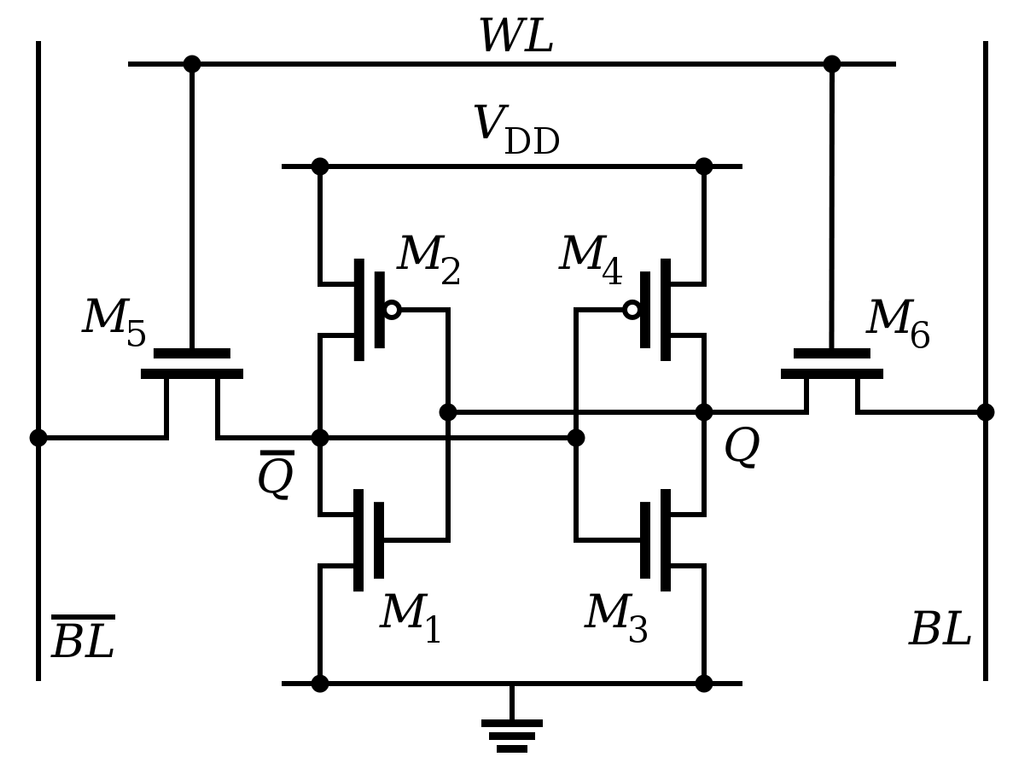

หน่วยความจำ RAM ปัจจุบันทั้งหมดที่ใช้ภายนอกโปรเซสเซอร์เป็นประเภท DRAM หรือ Dynamic RAM ในขณะที่หน่วยความจำที่ใช้ภายในโปรเซสเซอร์คือ Static RAM หรือ SRAM ทั้งสองทำงานเหมือนกันมากในแง่ของวิธีการเข้าถึงข้อมูล แต่สิ่งที่ไม่เหมือนกันคือวิธีการจัดเก็บหน่วยความจำเล็กน้อย

หน่วยความจำ DRAM มีราคาถูกกว่ามาก แต่โดยธรรมชาติแล้วต้องมีการรีเฟรชอย่างต่อเนื่องและความเร็วในการเข้าถึงช้ากว่า SRAM ดังนั้นโดยทั่วไปจึงไม่ใช้ภายในโปรเซสเซอร์ ในทางกลับกันมันปรับขนาดในทางที่แย่กว่า DRAM ดังนั้นแม้ว่า IBM จะใช้หน่วยความจำ DRAM เป็นแคชระดับสุดท้ายในซีพียูสำหรับการประมวลผลประสิทธิภาพสูง POWER ในรุ่นต่อไป แต่พวกเขาก็จะใช้ SRAM หน่วยความจำ.

ดังนั้นแนวคิดของแคชซึ่งเกี่ยวข้องกับหน่วยความจำประเภท SRAM ร่วมกับแนวคิด DRAM ในหลักการจึงไม่ตรงกันและแม้ว่าเราจะมีกรณีของซีพียูของ IBM แต่เราจะไม่พูดถึงการใช้หน่วยความจำ DRAM เป็นแคชภายใน โปรเซสเซอร์

DRAM cache และหน่วยความจำ HBM เป็นตัวอย่าง

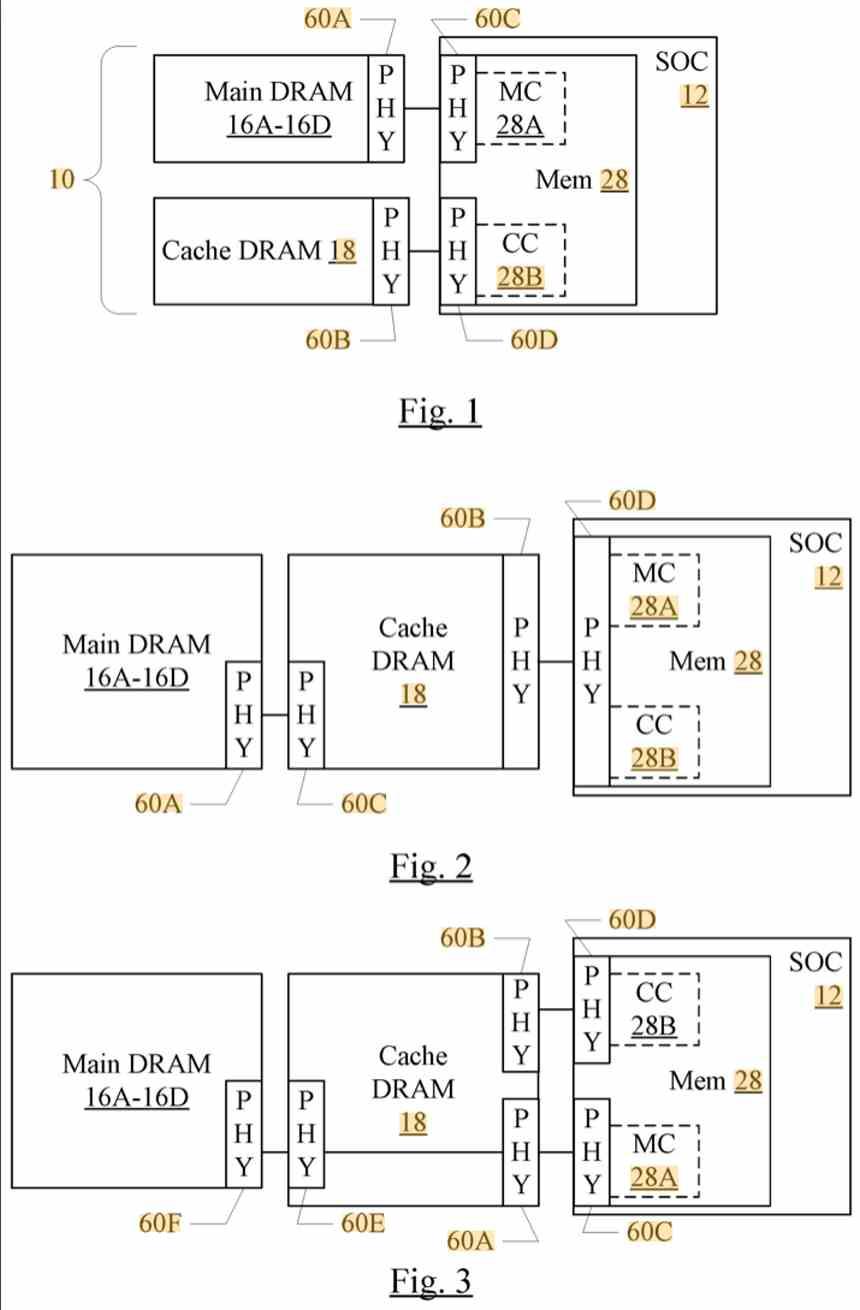

Cache DRAM เป็นแนวคิดของการเพิ่มเลเยอร์เพิ่มเติมในลำดับชั้นของหน่วยความจำระหว่างแคชระดับสุดท้ายของโปรเซสเซอร์และหน่วยความจำระบบหลัก แต่สร้างผ่านหน่วยความจำ DRAM ที่มีความเร็วในการเข้าถึงสูงกว่าและมีเวลาแฝงน้อยกว่า DRAM ที่ใช้เป็นหน่วยความจำหลัก

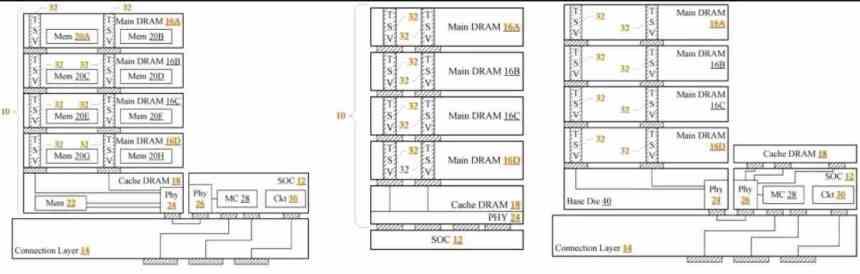

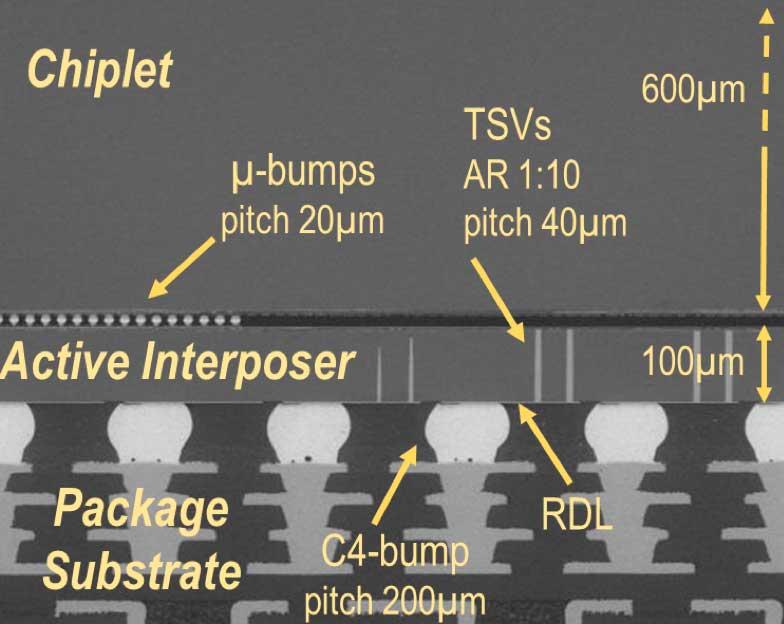

วิธีหนึ่งในการบรรลุเป้าหมายนี้คือการใช้หน่วยความจำประเภท HBM เป็นแคช DRAM ซึ่งเป็นหน่วยความจำ DRAM ประเภทหนึ่งที่ชิปหน่วยความจำต่างกันจะซ้อนกันและเชื่อมต่อในแนวตั้งโดยใช้สายเคเบิลประเภทที่เรียกว่า TSV หรือเส้นทางผ่าน ซิลิคอนโดยข้อเท็จจริงที่ว่ามันผ่านชิป การเชื่อมต่อประเภทนี้ยังใช้สำหรับการสร้างหน่วยความจำ 3D-NAND

เนื่องจากการเชื่อมต่อเป็นแนวตั้งจึงจำเป็นต้องมีตัวประสานซึ่งเป็นชิ้นส่วนอิเล็กทรอนิกส์ในรูปแบบของบอร์ดที่รับผิดชอบในการสื่อสารโปรเซสเซอร์และหน่วยความจำ HBM ทั้งโปรเซสเซอร์ไม่ว่าจะเป็น ซีพียู or GPUติดตั้งอยู่บนตัวประสานดังกล่าวซึ่งเนื่องจากระยะทางสั้นทำให้หน่วยความจำ HBM สามารถทำงานเป็นหน่วยความจำ DRAM ประเภทหนึ่งที่มีเวลาแฝงต่ำกว่าหน่วยความจำ DDR และ GDDR แบบคลาสสิก

ควรชี้แจงว่าหาก DRAM อยู่ใกล้โปรเซสเซอร์มากขึ้นเนื่องจากการกำหนดค่า 3DIC วางไว้เหนือระดับนั้นระดับเวลาแฝงเมื่อเทียบกับหน่วยความจำ HBM จะต่ำกว่าและความเร็วในการเข้าถึงจึงสูงขึ้นเนื่องจากอิเล็กตรอนมี เพื่อเดินทางในระยะทางที่สั้นลง

เราได้ใช้หน่วยความจำ HBM เพื่อให้คุณคิดได้จริง ๆ แต่หน่วยความจำประเภทใดก็ได้ในการกำหนดค่า 2.5DIC จะเป็นตัวอย่าง

แต่ผู้แทรกแซงมาตรฐานไม่เพียงพอ

ปัญหาต่อไปคือแคชไม่ทำงานในลักษณะเดียวกับหน่วยความจำ RAM เนื่องจากสิ่งที่ระบบค้นหาข้อมูลของโปรเซสเซอร์ไม่ได้คัดลอกบรรทัดคำสั่งจาก RAM ทีละบรรทัด แต่เป็นระบบหน่วยความจำแทน สิ่งที่แคชทำคือคัดลอกส่วนของหน่วยความจำโดยที่บรรทัดของโค้ดปัจจุบันอยู่ในระดับสุดท้ายของแคช

ระดับสุดท้ายเก็บแคชของโปรเซสเซอร์จะแชร์โดยคอร์ทั้งหมด แต่เมื่อเราเข้าใกล้ระดับแรกมากขึ้นสิ่งเหล่านี้จะเป็นส่วนตัวมากขึ้น ควรชี้แจงว่าแต่ละระดับแคชมีส่วนของแคชก่อนหน้าตามลำดับจากมากไปหาน้อย เมื่อโปรเซสเซอร์ค้นหาข้อมูลสิ่งที่ทำคือค้นหาตามลำดับจากน้อยไปหามากของระดับแคชซึ่งแต่ละระดับมีความจุมากกว่าระดับก่อนหน้า

แต่เพื่อให้หน่วยความจำ HBM ทำงานเหมือนแคชเราจำเป็นต้องมีองค์ประกอบที่สื่อสารโปรเซสเซอร์กับหน่วยความจำดังกล่าวซึ่งก็คือตัวประสานเพื่อให้มีวงจรที่จำเป็นในการทำงานเหมือนหน่วยความจำแคช ดังนั้นจึงไม่สามารถใช้ interposer แบบเดิมได้และจำเป็นต้องเพิ่มวงจรเพิ่มเติมในตัวประสานที่ช่วยให้หน่วยความจำ HBM ทำงานเหมือนแคชหน่วยความจำเพิ่มเติม