RAM メモリは 70 年代からすべてのコンピュータに搭載されてきましたが、コンポーネントがどのように現れたり消えたりするかを見てきました。 廃用によるものもあれば、他のものに統合されたものもあります。 ただし、プロセッサの隣にはまだあります。 しかし、もし プロセッサ内にRAMを統合しました 消えた? これは可能ですか? ご説明いたします。

ハードウェアの傾向として、マザーボードは数年前に比べてシンプルになっています。 数年前から、人々は RAM と CPU 同じエンティティにマージします。 将来それが見られるでしょうか、それとも制限がありますか?

プロセッサ内に RAM を統合することは可能ですか?

プロセッサのパフォーマンスに関する概念の XNUMX つは、メモリが命令を実行するユニットに近いほど、命令を解決するのにかかる時間が短くなるため、パフォーマンスが向上するというものです。 理由? 簡単に言えば、電気信号の移動距離が短くなります。 したがって、プロセッサとメモリが同じチップ上にあることが理想です。

ただし、すべてのプロセッサがプログラムを実行するために使用するサポート メモリである RAM メモリがあるという事実に気付きます。 ご存知のように、これはチップの外側にあるため、理想的なパフォーマンスをもたらしません。 それだけでは不十分であるかのように、この距離はデータ送信時のエネルギー消費を増加させます。

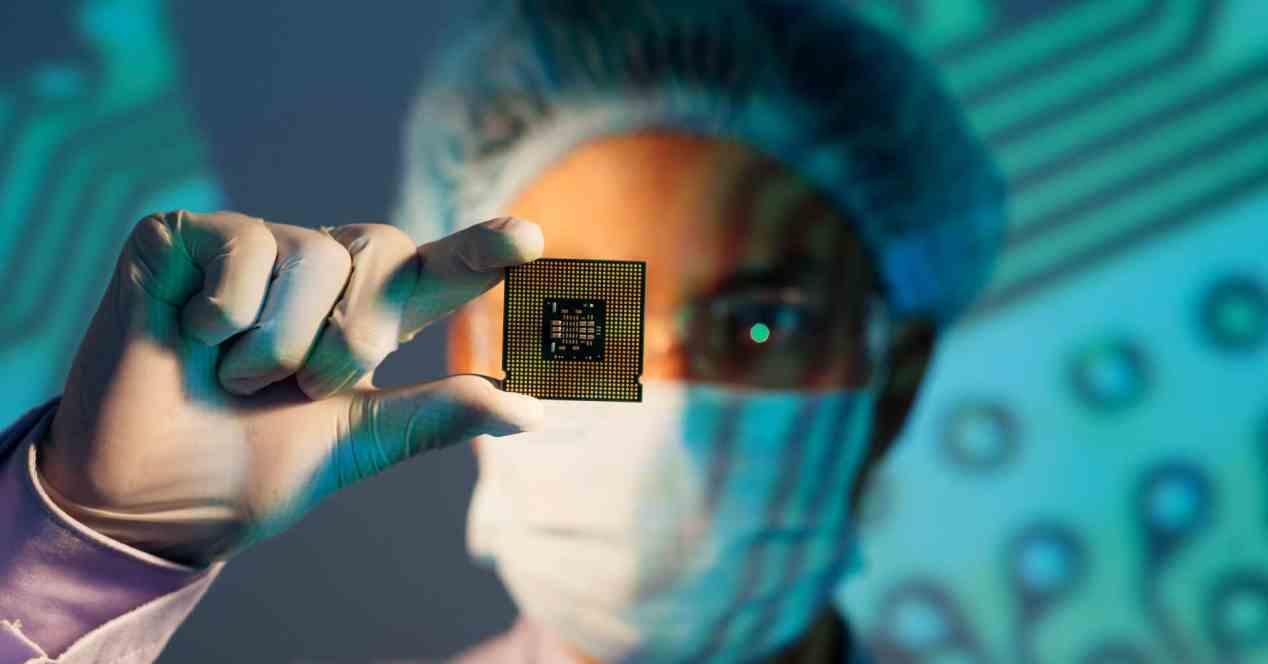

RAM メモリはあらゆるアーキテクチャの基本的な部分であり、削除できないことを念頭に置いて、このコンポーネントをビューから削除するとどうなるか疑問に思いました。 つまり、プロセッサに統合した場合です。 いずれにせよ、マイクロコントローラはチップ内で動作するメモリを正確に持っているため、このタイプのチップはすでに存在しますが、その機能は非常に限られています。

プロセッサ内に RAM を統合する利点

まず、RAM をプロセッサに統合する利点について説明します。 これまでのところ、製造業者がそれを行うことを妨げる技術的な制限を考慮に入れるつもりはないため、条件付きにしました。 これについては後で入力します。 したがって、当面は、理論上の概念と、それによってもたらされる利点に限定します。

BMIが消える

統合メモリ コントローラは、外部メモリとのアクセスを管理する役割を担っており、そのスペースはプロセッサ内の RAM メモリによって占有されるため、最終的には姿を消すことになります。 同様に、システムのメモリと外部との通信を担当するインターフェースであるペリフェラルの全体の部分も、メモリが理論上存在しないため、存在しなくなります。

プロセッサのパフォーマンスが向上します

明らかに、データと命令へのアクセス時間を完全に短縮することにより、それらすべてがより短い時間で実行され、明らかにこれらのパフォーマンスは、特定の時間内に実行できる命令の数によって測定されます。 なんで? まあ、これはプログラムをより速く実行することに変換されるか、それが失敗すると、それらのいくつかを同時に管理できるという事実のために.

消費が減る

プロセッサ内でビット データを送信すると、現在 0.1 pJ/ビットのエネルギー コストがかかります。これを DDR5 に送信すると、7 pJ/ビットのコストがかかります。つまり、エネルギー消費は最大 70 分の XNUMX に削減されます。 データ通信に関する限り。

キャッシュが消えない

キャッシュの役割は、情報の一時的なコピーを RAM に保持することですが、チップ内に保持することで、取得にかかる時間が短縮されます。 ランダム アクセス メモリをチップ内に配置すると、遅延が少なくなり、キャッシュ レベルを高くする必要がなくなることがわかります。 したがって、理論的には、キャッシュ ユーティリティをロードします。 ただし、これは完全に当てはまるわけではなく、問題が発生する可能性があります。

キャッシュには、各コアの最下位レベルにローカル コピーを配置することでメモリ アクセスのブロックを減らすという XNUMX 番目のユーティリティがあることを考えると、キャッシュがなければ、膨大な数のデータが原因でデータ バスに輻輳の問題が発生します。なる要求。 つまり、すべてのプロセッサにメモリ プールがあり、ローカル バックアップがない場合、過剰なアクセスによってパフォーマンスに負担がかかります。

そのため、少なくとも XNUMX レベルのキャッシュ、つまり最初のレベルが必要になります。これは通常、データと命令に分割され、レイテンシが最小のレベルです。 複数のコア間ですでに共有されている中間キャッシュ レベルを追加することは可能ですが、設計者は、そのレイテンシがプロセッサの統合 RAM よりも低いことを確認する必要があります。

では、なぜそれが行われていないのですか?

なぜキャッシュ メモリについて説明したのかと不思議に思われる方もいるかもしれませんが、その理由の XNUMX つはチップ上のスペース不足にあるからです。 ご存知のように、プロセッサを製造する場合、それを販売したい人は誰でも、利用可能なウェーハの数、ウェーハあたりのプロセッサの数、およびコストを考慮する必要があります。 RAM メモリの DIMM または SO-DIMM を取り、そこにあるすべてのチップを見てください。プロセッサの内部に収まると思いますか? いいえ、できません。

そのため、RAM メモリとプロセッサを製造するために使用される方法は、時間の経過とともに変化し、今日ではプロセッサに特化した TSMC のようなファウンドリーは、メモリとプロセッサの製造に関して際立っていません。 逆に。 両方のタイプのチップを同時に組み合わせることを可能にするプロセスを見ることは非常に困難です, 家庭用システムではめったに見られない、経済的に正当化される開発中のチップがない限り.

プロセッサー内の RAM の代替品

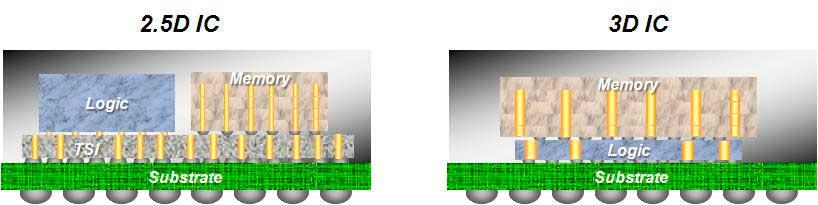

代替手段は、新しい方法を使用して、シリコンを介したビアに基づいて集積回路を構築すること以外に何もありません。プロセッサを RAM と並べて配置し、両方をインターポーザーにマウントします。これは 2.5DIC として知られ、既に見たHBM メモリを搭載したシステムで。 もう 3 つの解決策は、プロセッサまたは XNUMXDIC の上に RAM チップを積み重ねることです。 問題? これらの方法の追加コストは非常に高いため、国内市場では実行できませんが、どちらの場合も提供されるメモリは、従来の RAM よりもレイテンシと消費が低くなります。

サーバー プロセッサの市場では、間もなく HBM メモリを使用した構成が見られるようになります。問題は、サイズが固定されており、より大きな RAM が必要な場合は、従来の RDIMM ソケットを捨てる必要があることです。 これにより、RAMをプロセッサに統合することが完全に破壊され、システムにRAMを実装する必要がなくなります。 いずれにせよ、これらのソリューションは、RAM をプロセッサに完全に統合するよりも、データ アクセスに関してレイテンシや消費を削減するものではありません。