Apple TSMC 5nmの配信がクラッシュし、A14と将来のKirin 9XXXのパフォーマンスが見られました。どちらの場合も、パフォーマンスはほとんど向上せず、消費量はほとんど削減されておらず、一般に、改善は予想よりも少ないようです。 、エアワープについての質問、N5はTSMCの故障ですか? 何が AMD 高性能バージョンが期待される改善を達成しない場合はどうしますか?

TSMCは、多くのセクターで現在のスターノードであるため、すべての領域で7nmで勝利を収めたと言えます。 しかし、特にAppleやAppleなどの多くのSoCの測定値を考慮すると、N5はそれほど見栄えがよくありません。 Huawei社、 何が起こっている?

高性能ではないプロセスのごくわずかな改善

A14で見たので、Appleはどうなっているのだろうと思いました。 質問が本当にあるとき、何が起こっているのか TSMC N5 ? アップルチップの改良点、初の独占 ARM 同様に排他的なノードを持つバージョンは、私たちを冷たくしました。 チップ自体が悪いわけではないので、そうではありませんが、アーキテクチャ変更後のA13と比較した改善とナノメートルの飛躍により、すべての分野ではるかに高いパフォーマンスを考えました。

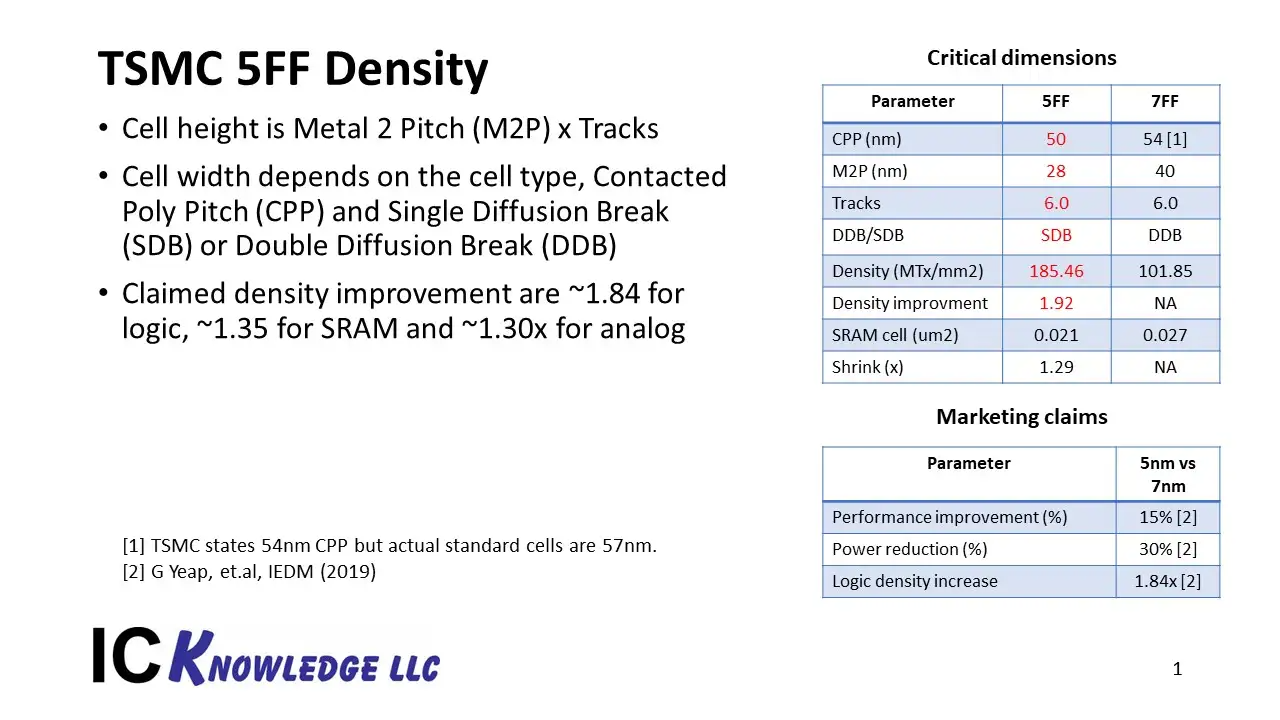

問題はEUVに由来するようであり、層の数が多いと、先験的に問題とは思われなかったことが妨げられ、効率とパフォーマンスが向上するだけです。 歴史的に、Appleは常に少なくとも到達することを自慢してきました の90% 理論的な 密度 それが機能していたノードの、しかしA14では、尋ねられるまでそれについてのレビューはありませんでした。

いくつかのインタビューの後、14nmのA5は達成しただけであることが判明しました 78%の実効トランジスタ密度 、これはチップ全体の深刻な全損失を意味します。

FinFETを継続するためにN5ノードの大失敗に直面していますか?

明確ではありません。レイヤーの数が最も多い可能性があります。FinFETがEUVで最適化されていない可能性があり、その数のレイヤーであるか、Appleがノードに適応していない可能性があります。 いずれにせよ、TSMC自体が1.84Xの削減について話していたが、A14は1.49Xをはるかに下回っていることを覚えておく必要があります。

インテル & サムスン はすでにナノシートでGAAを使用しており、TSMCはFinFETを3nmの耐用年数の限界まで引き上げています。 5nmが移行ノードであり、高性能バリアントで同じ問題が発生する場合、7nmに対して大きな変化がなければ、AMDはこのノードの使用を再考する必要があります。

インテルは強力になっていることを覚えておく必要があります 10 nm スーパーフィン 、AMDは+なしで3nmでZen2とRDNA7を起動する必要があり、最終的に7 nmの高性能をスキップした場合、EUVはそれらの5nmでの一時的な解決策になる可能性があります。

そして、私たちが見ているようにすべてが密度であるわけではありません。セルの設計、高さ、ゲート、および無限の接続数は、XNUMX平方ミリメートルあたりのトランジスタ数を増やすことと同じくらい重要です。