より多くのコアを持つプロセッサを選択するという事実 特定のプログラムを使用する場合、多くの場合、同じ程度のパフォーマンスの向上にはなりません。 なぜこの現象が発生し、その原因は何ですか? 詳しくご説明いたします。

時間の経過とともに新しいバージョンのプログラムを使用する理由の XNUMX つは、コア数の多いプロセッサをより有効に活用するように設計されていることです。 時間の経過とともに、CPU 内のこれらの数が増加していることを忘れないでください。 しかし、プログラムのパフォーマンスが同等に向上しないのはなぜでしょうか?

プログラムはコアの数に合わせてスケーリングすることはありません

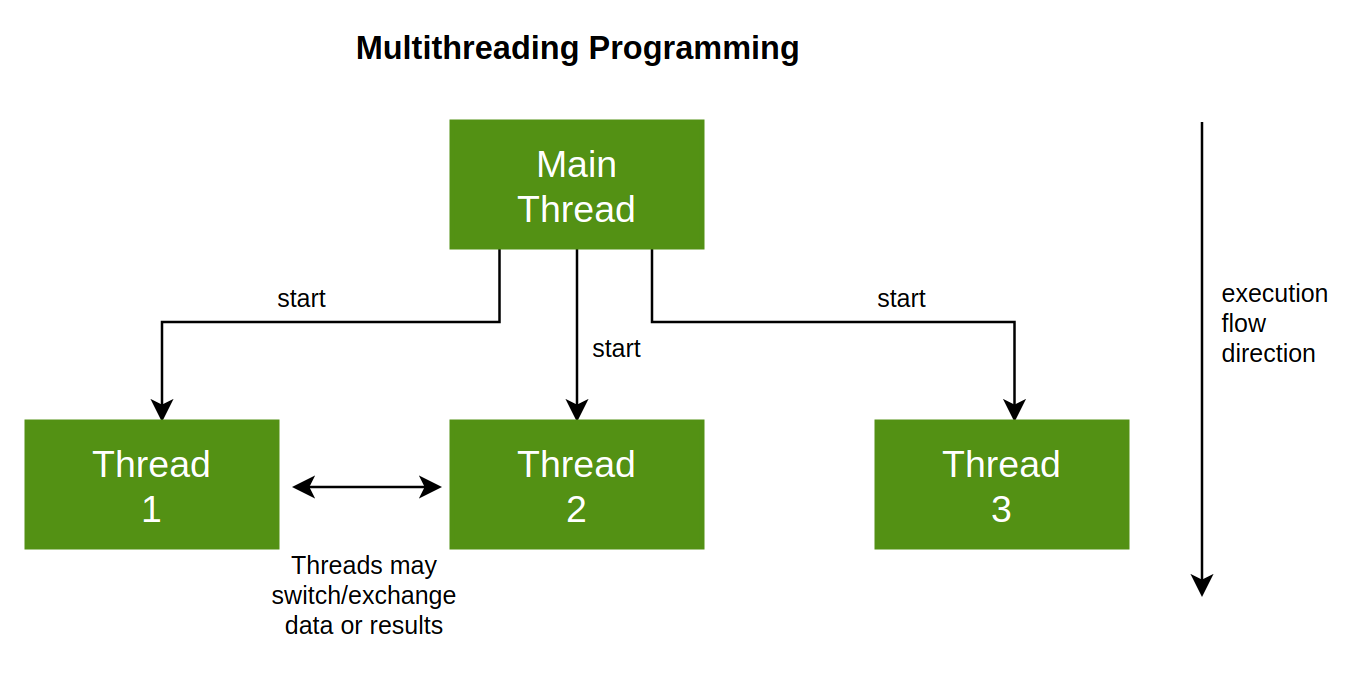

実行されるプログラムには、実行スレッドの数に応じて、アクティブなプロセスまたはタスクをいつでも分割する機能がないことを考慮することが重要です。 CPU. 何よりも、この分割がプログラム コードで明示的であるという事実、つまり、プログラマのスキルとアプリケーションの設計の産物であるという事実によるものです。

実際、プログラムをコーディングする際に重要なのは、可能な限り多くのコアを使用するためにプログラムを最適化することではなく、レイテンシーを最適化することです。 後者は、プロセッサがタスクを完了するのにかかる時間であり、時間単位で測定されます。 そして、CPU のパフォーマンスは、可能な限り短い時間で多くのタスクを完了することから成り立っているということです。 どちらが最初にアーキテクチャに依存し、次にクロック速度に依存します。

ただし、レイテンシーに関して私たちが興味を持っているのは、特定の期間内に完了することができるタスクの数を知ることです。これはワークロードであり、これは状況とプログラムの作成方法によって異なります。 つまり、パフォーマンスはハードウェアだけでなく、ソフトウェアの書き方の良し悪しにも左右されます。

いくつかのコアでの分業

ここで、システムのコア数を増やすと、作業を細かく分割して完了することがはるかに簡単になります。 ここで、T/N 式が登場します。ここで、T は実行するタスクの数であり、N はシステムが実行できる実行スレッドの数です。 明らかに、少数のコアに最大数のジョブをロードし、力ずくで修正することができます。 問題は、この方法が逆効果であることです。これは、各コアで個別に高いパフォーマンスを発揮する最新の CPU にメリットがあるためです。

ただし、異なるコア間で作業を分割することは、通常、導体として機能するコアに与えられ、次のタスクを実行する必要がある追加の作業です。

- プロセスとタスク リストを作成し、常に適切に管理する必要があります。

- 彼らは、タスクの開始と終了を常に予測する方法を知っている必要があります。これには、タスクを終了して別のタスクを開始するのにかかる時間も含まれます。

- 異なるカーネルは、メイン カーネルにシグナルを送信して、プロセスの開始時と終了時を知る機能を備えている必要があります。

このソリューションは、ソニー、東芝、IBM のセル ブロードバンド エンジンに採用されました。セル ブロードバンド エンジンは、マスター コアが残りの処理を担当する PS3 の中央処理装置です。 ずっと前ですが、Atari Jaguar に採用されました。 PS4 の場合、SONY はこのモデルを二度と繰り返さず、悪夢であるため誰も PC に実装していませんが、作業を分割する最も効率的な方法です。

すべてが複数のコアで実行できるわけではありません

タスクをサブタスクに分割して、より多くのコアに無期限に分散できるかどうかを自問すると、答えはノーです。 具体的には、タスクを XNUMX つの異なるタイプに分類する必要があります。

- 完全に並列化できるため、中央処理装置が持つさまざまなコア間で分割できます。

- 部分的に並行して実行できるタスク。

- 並列実行できないコードの部分。

最初のケースでは、T/N が 100% に適用されます。XNUMX 番目のケースでは、コア数の増加による加速が部分的である、いわゆるアムダールの法則にすでに入っています。XNUMX 番目のケースでは、単純にすべてのそのタスクのためのシングルコアのパワー、

マルチスレッドにおける CPU と GPU の違い

ここで微分点に到達します。 GPU または、グラフィックス チップには、コマンド リストを読み取り、それらをさまざまな GPU コア間、さらにはさまざまなユニット間で配布する役割を担う制御ユニットがあります。 これは前のケースのハードウェア レベルの実装であり、作業がある限り飽和させたい任意の構成で完全に機能し、したがってできるだけ多くのコアをビジー状態に保ちます。 ただし、GPU での実行の概念スレッドは、対応するデータとその命令のリストに常に対応していることを理解する必要があります。 つまり、ピクセル、頂点、または任意のデータです。

これにより、並列化が容易になります。 つまり、卵を揚げる場合、CPU 内のプロセスは卵を揚げることであり、これは完全にシーケンシャルになります。 一方、グラフィックス チップでは、タスクは単に油を加熱したり、フライパンに卵を追加したりするだけです。 これらすべてが XNUMX つの卵を揚げる速度を速めるわけではありませんが、複数の卵を揚げる速度は速くなります。そのため、数百万のポリゴンやピクセルを同時に計算するようなタスクには GPU が適していますが、シーケンシャル タスクには適していません。