CPU内にRAMを統合することは可能ですか? それはどのような利点をもたらしますか? 将来的に見られる可能性はありますか? 最も興味深いアイデアのXNUMXつは、RAMをプロセッサのできるだけ近くに配置することです。 これがどのように可能になるか、そしてそれが実現された場合、それがPCのハードウェアとそれが実行するプログラムにどのように影響するかを説明します。

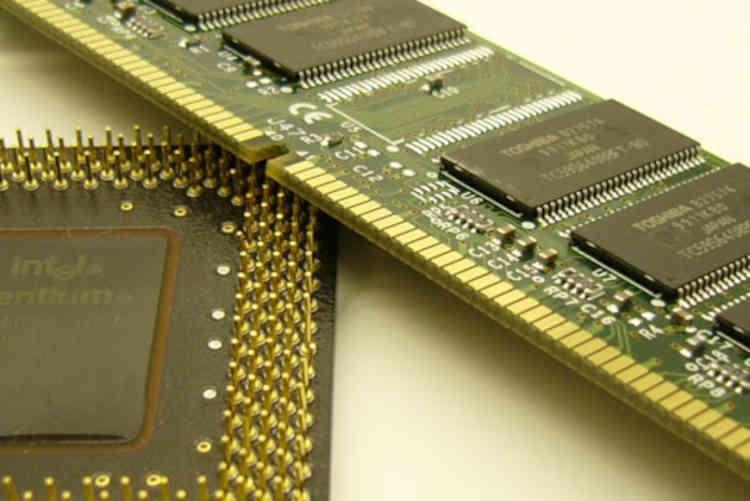

2003年に、重要なプロセッサに関する限り、最も重要な改善のXNUMXつが行われました。それは、それまでプロセッサの外部にあったプロセッサ内部のノースブリッジの実装です。 ノースブリッジは、マザーボード上のCPUおよびその他のプロセッサをRAMと通信する部分です。

統合に向けた次のステップは? おそらくRAMまたはその少なくとも一部をCPU内に統合します。

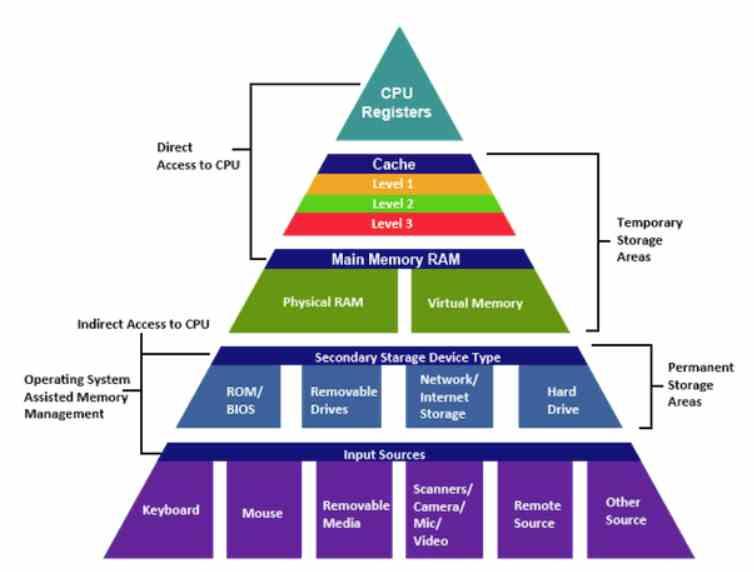

データまでの距離はパフォーマンスに影響します

プロセッサのパフォーマンスに関する基本原則のXNUMXつは、データを格納するメモリとデータを処理するユニットの間の距離です。電気信号ははるかに短い距離を移動する必要があるため、短いほど良いです。これは、命令の実行時間の短縮につながります。

そのため、第XNUMXレベルのキャッシュでアクセスできるデータは、RAMにあるデータよりも高速に実行されます。 理想的には、プロセッサの近くに大量のメモリを配置できます。

ただし、スペースが限られており、RAMをプロセッサの隣に配置すると、両方に悪影響を及ぼし、両方が非常に高温になり、両方のパフォーマンスの合計が以下になる可能性があるため、これを行うことはできません。両方を別々に。

3DICテクノロジーを利用してRAMをプロセッサーに統合

3DICテクノロジーがメモリチップの複数のスタックを組み合わせているのを見てきましたが、特にPCではCPUとメモリを組み合わせていません。 たとえば、HBMメモリは当初、プロセッサの上にマウントするように設計されていましたが、到達した温度が非常に高かったため、両方の当事者のクロック速度を下げる必要がありました。

サムスンのスマートフォンでは、512MhzのSDRタイプの200ビットシリコンチャネルを介した垂直インターフェイスで構成されるWideI / O標準を利用しようとしています。 わずか12.8GB / sに達しましたが、当時のLPDDRメモリと比較してレイテンシとエネルギー消費が少ない代替手段と見なされていました。 問題? それはコストを増加させたので、業界によって拒否されました。

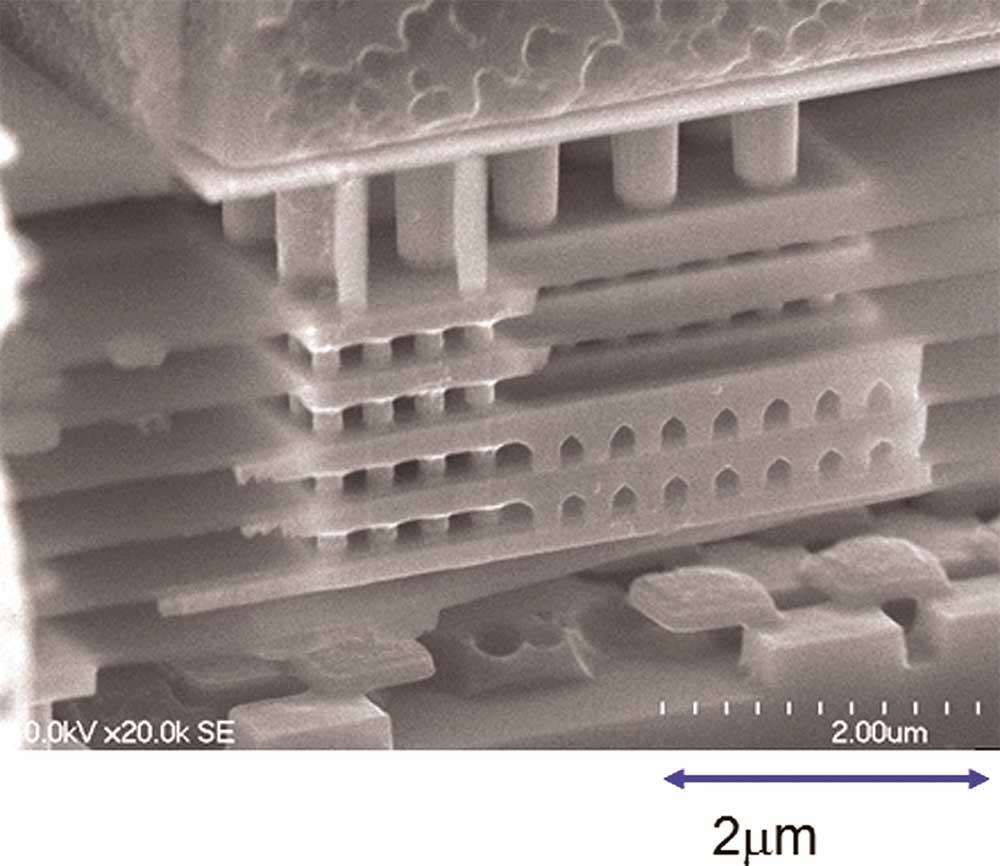

このソリューションはとらえどころのないことが証明されていますが、3DICシステムの利点のXNUMXつは、組み込みメモリの密度の問題を解決できることです。

組み込みメモリ容量の問題

DRAMメモリの密度はSRAMの3倍ですが、問題は40nmを超えるとプロセッサ内にDRAMメモリを実装できないため、SRAMメモリを利用する時期になりました。 問題は、SRAMメモリが高密度であっても、プロセッサ内に十分なRAM密度を収めることができないことです。

最も単純なロジックは、RAMのみのチップを3DICテクノロジを搭載したプロセッサの上に配置する場合、密度を上げる必要があることを示しています。問題は、メモリ密度を上げるには、巨大なメモリスタックが必要になり、メモリが増えることです。もっと高い。 プロセッサであり、実行可能ではありません。

しかし、解決策があります。RAMを異なる階層のXNUMXつの異なるメモリウェルに分割します。

XNUMXつのRAMウェル、XNUMXつはプロセッサに統合され、もうXNUMXつはDIMMに統合されています

コンセプトは、一方ではプロセッサに接続された十分なRAMメモリを持ち、レイテンシが非常に低く、帯域幅がはるかに速いというものです。 一方、一生に一度のクラシックRAMメモリモジュールにはクラシックRAMメモリがあります。

アイデアは、オペレーティングシステムを介して、システム内の異なるRAMウェルの使用を割り当てることです。これらには、XNUMXつのメモリウェルは表示されませんが、アドレス指定の唯一の違いが正確に書き込むメモリアドレスであるXNUMXつだけです。各プログラムをダウンします。