26日 TSMC テクノロジーシンポジウム、メーカーは、7 nmノードN7、および3 nm N5、N4、N3ノードでの進捗状況の最初の詳細を説明しました。 TSMCはまた、新しい 3DFabricテクノロジー それを超えてスケーリングを継続するために使用するテクノロジーについての手がかりを提供しました 3nm ノード。 この記事では、TSMCがすでに検討している、このエースアップスリーブがどのように機能するかを説明します。 インテル バックミラーで。

TSMCは、Intelを迂回し、半導体業界の階層をすでに崩壊させました。 サムスン 業界をリードする7nmノードに移行し、Intelの競合他社を推進しました(AMD とりわけ)ヴァンガードに。 それでも、同社はイノベーションの急速なペースを鈍化させる兆候は見られず、3年までに2022nmテクノロジーの量産を開始する予定です(これを視野に入れると、Intelは7年末または2022年初頭までに2023nmテクノロジーを導入する予定です。 )。

TSMC製造プロセス

TSMCの 5nm N5プロセスは EUVテクノロジー 「広範囲」であり、7nm N7に比べてリソグラフィーのスケーリングに期待される利点を提供します。 TSMCは、N5プロセスは、(同じ消費で)最大15%高いパフォーマンス、または同じパフォーマンスで消費を30%削減できると主張しています。 論理密度 利得 N1.8プロセスの7倍 。 彼らはまた、N5の欠陥密度学習曲線はN7よりもはるかに速いと主張しています。これは、このプロセスがより高いスループットレートに到達し、以前のプロセスよりも速くなることを意味します。

| N5上のN7(7nm) | N5上のN5P | N4上のN5(5nm) | N3(3nm)上のN5(5nm) | |

|---|---|---|---|---|

| 同等のパフォーマンスを実現するパワー | 視聴者の38%が | 視聴者の38%が | ? | 25-30% |

| 同じ消費量でのパフォーマンス | XNUMX% | 5% | ? | 10-15% |

| 密度の向上 | 1.8X | ? | ? | 1.7X |

| リスク/大量生産 | 生産中 | 2021ことで | 2022 | 2022の後半 |

TSMCには、高性能アプリケーション用に開発中の拡張ノードN5Pもあり、2021年に量産を計画しています。N5Pは5%以上のパフォーマンスまたは 消費量を10%削減 N5以上。 同社によると、彼らはすでに次のサーバーチップをN5プロセスに導入しているため、TSMCが5nmのほとんどの設計ハードルをすでにクリアしていることは明らかです。

ノードN5のサポートにより、 5nm N4プロセス まだ見積もられていないパフォーマンス、電力、密度の改善により、移行が容易になります。 TSMCは詳細については詳しく述べていませんが、製造プロセスで必要なレイヤーが少ないことがわかっており、4年の第2021四半期にハザード生産を開始し、2022年までに大量生産を計画しています。

同社はまた、 3nmのN3ノードは 2021年にリスクの生産を開始し、2022年の後半に量産に到達します。このノードは、N5を超える完全なノードスケーリングを提供し、密度とともに10〜15%のパフォーマンス向上、または25〜30%の消費削減をもたらします最大1.7Xの改善。 ノードは引き続きFinFETアーキテクチャを使用し、SRAM密度が1.2倍、アナログ密度が1.1倍増加しています。

3nm未満のノードはシリコンの代替品を探します

TSMCは、N3を超えた次のノードの定義にも取り組んでおり、3nmを超えて到達するのに役立つ可能性のある業界の進歩を共有していますが、使用するテクノロジーの名前は示していません。 彼らは、高移動度チャネル、2Dトランジスター、カーボンナノチューブなどの新しい材料の使用とともに、ナノシートとナノワイヤーをすでに調査中の候補としてリストアップしました。

TSMCはナノシート技術で15年以上の経験があり、32Vで動作する0.46MbナノシートSRAMデバイスを製造できることを示しています。 彼らはまた、2 nmに適した非シリコン材料をいくつか特定しました。これにより、チャネルの厚さが1 nm未満であっても拡大縮小できます。 もちろん、 カーボンナノチューブは 彼らの計画の一部でもあります。

このため、同社は調査を深め続けており、2.96年だけで2019億ドルの投資がそれを証明しています。 彼らは本社の隣に8,000人のエンジニアを擁する新しいR&Dセンターを建設中であり、このプロジェクトの第2021段階はXNUMX年に完了する予定です。

3DFabric、TSMCの袖のエース

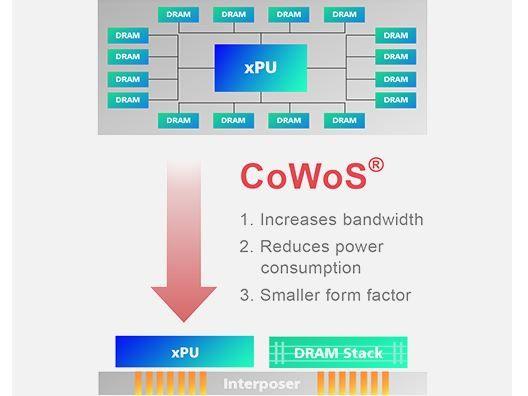

TSMCは、他の業界関係者からすでに聞いたことを反映して、高度なパッケージングテクノロジーが高密度化の鍵であり、3Dパッケージングテクノロジーが進むべき道であると信じています。 そこで登場するのが3DFabricテクノロジーです。

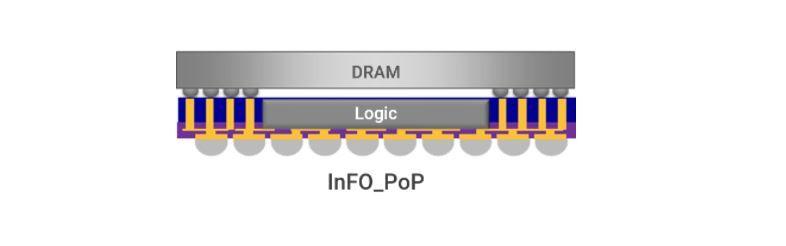

TSMCは、ウエハーレベルの3DICテクノロジーであるCoWoS(チップオンウエハーオン基板)、InFO-R(統合ファンアウト)、COW(チップオンウエハー)、WoW(ウエハー)の3Dパッケージングテクノロジーの強力なポートフォリオをすでに持っています。ウェーハ上)。 同社は現在、これらのテクノロジーを3DFabricという名前で実装しようとしています。これは、チップレット、高帯域幅メモリ、特殊IPを異種パッケージにバインドする3Dパッケージングテクノロジーの新しいブランディングスキームのようです。

つまり、3DFabricは要するに、TSMCが3 nmのノードとその後のノードの両方で機能するさまざまなテクノロジをすべて含む一種の「ファミリ」であり、ダウンすることができると予測しています。このテクノロジーを使用して1 nmからでも。