RAM Mémoire est l'un des composants essentiels de notre ordinateur, cependant, il a connu une évolution ennuyeuse ces dernières années depuis l'apparition de la mémoire DDR en 2000, depuis lors, nous avons vu jusqu'à quatre générations de cette mémoire et nous en avons une cinquième autour du coin. Mais que sera le La RAM du futur ressemble à et quels changements aura-t-il?

Nous sommes habitués à une mémoire RAM évoluant tous les x ans sous la forme d'une nouvelle génération de mémoire DDR, GDDR ou quel que soit le type de mémoire utilisé à un moment donné, mais cela pourrait changer car l'utilisation de certaines technologies sera nécessaire pour qu'il continue d'évoluer.

Comment la RAM a-t-elle évolué pendant tout ce temps?

La RAM étant un semi-conducteur évolue suivant La loi de Moore et en même temps l'échelle Dennard, cela signifie que d'une part la densité des transistors augmente et avec elle la capacité de stockage de la mémoire, tandis que d'autre part la vitesse de communication est améliorée, ce que nous appelons la bande passante.

L'idée est très simple, dans chaque nouveau nœud de fabrication la tension nécessaire pour atteindre une vitesse d'horloge spécifique diminue, nous pouvons donc créer une RAM qui consomme la même chose et est plus rapide ou une autre qui est tout aussi rapide mais consomme beaucoup moins.

Mais le problème vient avec l'augmentation de la vitesse, puisque la bande passante de la RAM d'un système dépend de la consommation d'énergie de la communication entre la mémoire et le processeur auquel elle est attribuée, donc la quantité de largeur de bande avec chaque nouveau nœud est limité et cela se produit en ce que les sauts d'un type de mémoire DDR à un autre deviennent de plus en plus petits.

Et si nous ne pouvons pas faire évoluer davantage la RAM du système à l'avenir?

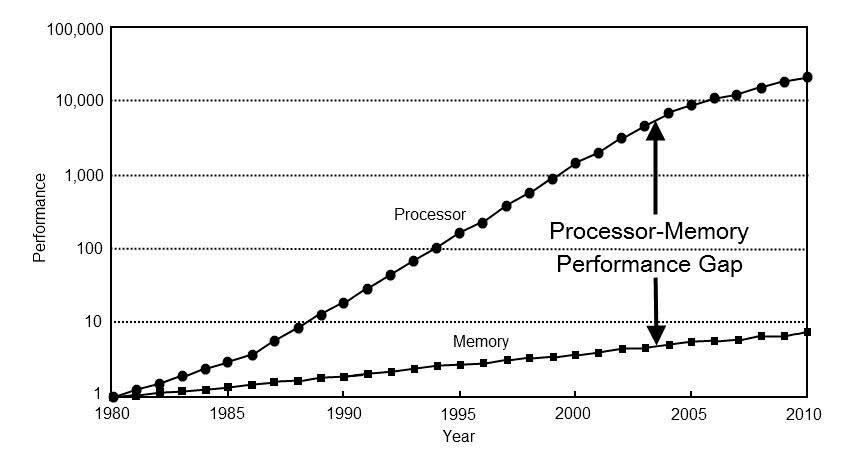

Avec chaque nouveau nœud de fabrication, utilisé pour fabriquer à la fois des mémoires et des processeurs, nous constatons que les sauts de vitesse d'horloge sont de plus en plus petits. Cela n'affecte pour l'instant que les processeurs, mais les souvenirs ne tarderont pas à les affecter et cela atteindra le point où un saut générationnel sera moindre que prévu, pour ne pas dire presque nul.

Avec chaque nouveau nœud de fabrication, utilisé pour fabriquer à la fois des mémoires et des processeurs, nous constatons que les sauts de vitesse d'horloge sont de plus en plus petits. Cela n'affecte pour l'instant que les processeurs, mais les souvenirs ne tarderont pas à les affecter et cela atteindra le point où un saut générationnel sera moindre que prévu, pour ne pas dire presque nul.

Une solution pour cela consiste à utiliser des technologies telles que PAM-4 utilisé dans le GDDR6X et les futures itérations du standard PCI Express, si on le regarde d'un certain point de vue, PAM-4 est toujours un type de compression de données. De plus, on dit que la future mémoire DDR6 pourrait utiliser la communication PAM-4.

Et en parlant de compression de données, il est très possible que nous voyions des mémoires RAM avec une logique à l'intérieur, des accélérateurs conçus pour rendre la recherche de données plus efficace et plus rapide, qui peuvent compresser et décompresser les données du vol qui est envoyé. La raison de cela est très simple, l'envoi de x octets qui sont des données compressées consomme de l'énergie de la même manière que l'envoi du même nombre d'octets avec des données non compressées.

Allons-nous voir la mémoire DRAM 3D comme la RAM du futur?

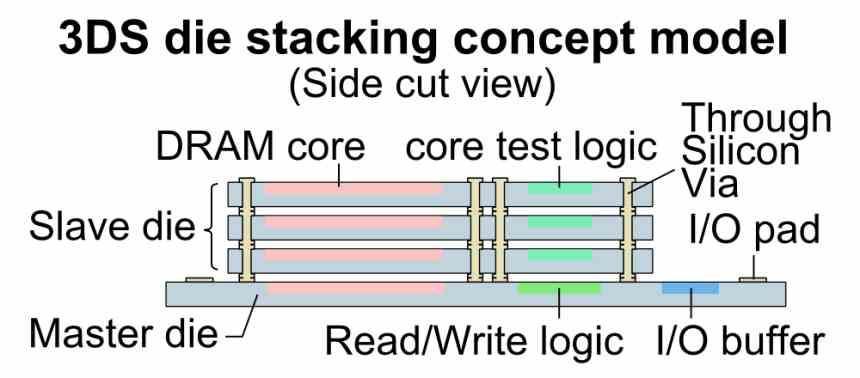

La DRAM 3D consiste à empiler plusieurs puces de mémoire et à utiliser des chemins à travers le silicium pour communiquer avec le contrôleur de mémoire.

Dans le cas des mémoires DDR, il existe des normes 3DS-DDR dans lesquelles jusqu'à 4 puces DDRn sont empilées (la nième génération de DDR) qui sont connectées à un contrôleur 64 bits. Ainsi, avec cette technologie, il serait possible de réduire un DIMM total de 8 puces à deux puces seulement. Mais cela n'apporte aucun avantage en termes de consommation et de rapidité, mais il en résulte une mémoire extrêmement coûteuse, ce qui a conduit à ne pas standardiser son utilisation et nous continuons avec les DIMM mémoires classiques.

La DRAM 3D n'a de sens que si elle est accompagnée d'interfaces avec un grand nombre de broches, qui peuvent transmettre un grand nombre de bits par cycle, permettant d'utiliser des vitesses d'horloge plus faibles et donc une tension plus faible, mais ces solutions nécessitent un interposeur complexe et limitent considérablement les capacités d'extension de la RAM.