Actuellement, les cartes graphiques conçues pour un usage domestique sont équipées de modules de mémoire GDDR6 et GDDR6X, sélectionnés pour leur combinaison optimale de performances et de rentabilité. Cependant, il convient de noter qu'il ne s'agit pas des options de mémoire exclusives disponibles pour les cartes graphiques, comme le démontrent des produits comme le AMD Série Radeon Vega. Notamment, SK Hynix a dévoilé une avancée significative dans le domaine de la mémoire des cartes graphiques avec l'introduction des modules HBM3E.

La technologie HBM (High Bandwidth Memory) n’est peut-être pas familière à tous, en particulier à ceux qui s’intéressent principalement aux graphismes de jeu. Les mémoires HBM se distinguent en offrant des taux de transfert de données nettement plus élevés que les mémoires GDDR plus courantes.

Cette capacité améliorée de transfert de données se traduit par des performances améliorées dans des cas d’utilisation spécifiques. Cependant, il est important de reconnaître plusieurs inconvénients associés à la technologie HBM. Le facteur de coût le plus important est le facteur de coût considérable, les modules HBM étant nettement plus chers, parfois même jusqu'à 20 fois plus chers que leurs homologues GDDR. De plus, ces modules sont positionnés à côté du GPU dans la même prise, entraînant des irrégularités de surface et des problèmes potentiels de dissipation thermique.

Présentation de la prochaine vague de technologies avancées de mémoire à large bande

SK Hynix a dévoilé sa dernière réalisation : la préparation à la production de ses modules pionniers HBM3E, avec des échantillons déjà envoyés à divers clients. Ces nouvelles puces introduisent un bond remarquable dans la vitesse de transfert de données, avec une vitesse impressionnante de 9 GT/s. Cette augmentation des performances équivaut à une amélioration notable de 40 % par rapport à l’itération HBM3 précédente.

La fabrication à grande échelle de ces composants de mémoire innovants devrait commencer au premier semestre de l'année prochaine. Les informations concernant les capacités spécifiques de ces nouvelles puces mémoire sont particulièrement absentes de la divulgation actuelle, et il n'existe pas non plus de données précises décrivant leur disponibilité pour les partenaires d'assemblage.

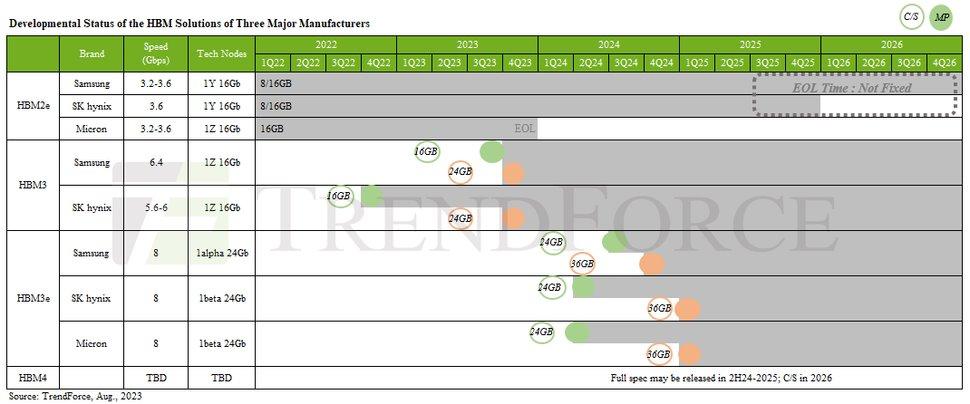

L'entité d'études de marché TrendForce a apporté ses idées en proposant des projections numériques. Selon leur analyse, SK Hynix a l'intention de produire des puces HBM24E de 3 Go au cours du premier trimestre 2024. Plus loin dans le calendrier, les plans s'étendent à la création de solutions de mémoire de 36 Go au cours du premier trimestre 2025.

Cette prévision de TrendForce s’aligne de manière fascinante sur les tendances actuelles du marché. Des anticipations circulent concernant NVIDIALe lancement prévu par Grace Hooper GH200 des solutions Grace Hooper GH2, destinées à l'IA et aux tâches informatiques avancées, est prévu pour le deuxième trimestre 2024. Les spéculations suggèrent que ces solutions GH200 pourraient intégrer 141 Go de mémoire SK Hynix HBM3E, bien que cela reste de nature spéculative.

Il est important de noter que les mémoires HBM3E de SK Hynix, bien qu'impressionnantes, ne revendiquent pas actuellement le sommet du marché de la mémoire. Cette nouvelle offre bénéficie d'une bande passante de 9 GT/s, légèrement derrière les unités de mémoire de Micron fonctionnant à 9.2 GT/s. Les solutions de Micron offrent une bande passante robuste de 1.2 To/s par pile, tandis que les offres de SK Hynix atteignent 1.15 To/s, soulignant la dynamique concurrentielle actuelle.

Conçu pour l'IA

Ce qui ajoute une tournure intrigante à la situation, c'est la décision de SK Hynix de rester discret sur les spécifications exactes de ces nouveaux modules de mémoire. Cependant, ils ont choisi de mettre l’accent sur leur utilisation de la technologie Advanced Mass Reflow Molded Underfill (MR-RUF). Cette innovation joue un rôle central dans la réduction des écarts entre les composants au sein d'une pile HBM, offrant simultanément une amélioration de 10 % de l'efficacité de la dissipation thermique. De manière impressionnante, cette technologie parvient également à maintenir la même hauteur Z pour une configuration 12 Hi HBM2 qu'un module 8 Hi HBM.

Un élément de curiosité entourant la norme HBM3E vient de son manque actuel de validation par le JEDEC, l'organisme de réglementation établi responsable de la certification et de la validation des puces mémoire. Il convient de rappeler que le respect des normes JEDEC est habituel pour les composants de mémoire.

Le rythme accéléré des développements pourrait potentiellement être attribué aux demandes du marché, en particulier à l’essor de la production de masse pour les applications d’IA et de calcul haute performance. Dans ce contexte, il est concevable que la production de masse commence avant de recevoir la certification officielle, ce qui pourrait constituer la première apparition d'un tel scénario. Cela pourrait signifier une rupture avec la séquence conventionnelle où la production de masse suit habituellement après la validation réglementaire.