Vous avez sûrement entendu (ou lu) parler de la Code de correction d'erreur ECC dans de nombreux composants matériels, tous liés à la mémoire (soit RAM ou stockage), bien que très peu comprennent son importance. Pour cette raison, dans cet article, nous allons expliquer comment l'ECC fonctionne dans un SSD contrôleur , et comment grâce à cela il est possible d'augmenter la longévité et de faire une grande différence dans le durée de vie utile des SSD .

Chaque périphérique qui utilise la mémoire Flash NAND nécessite un code de correction d'erreur de bit aléatoire (connu sous le nom d'erreur «logicielle»). C'est parce que beaucoup de bruit électrique est produit à l'intérieur d'une puce NAND et les niveaux de signal des bits qui traversent une chaîne de puces NAND sont très faibles.

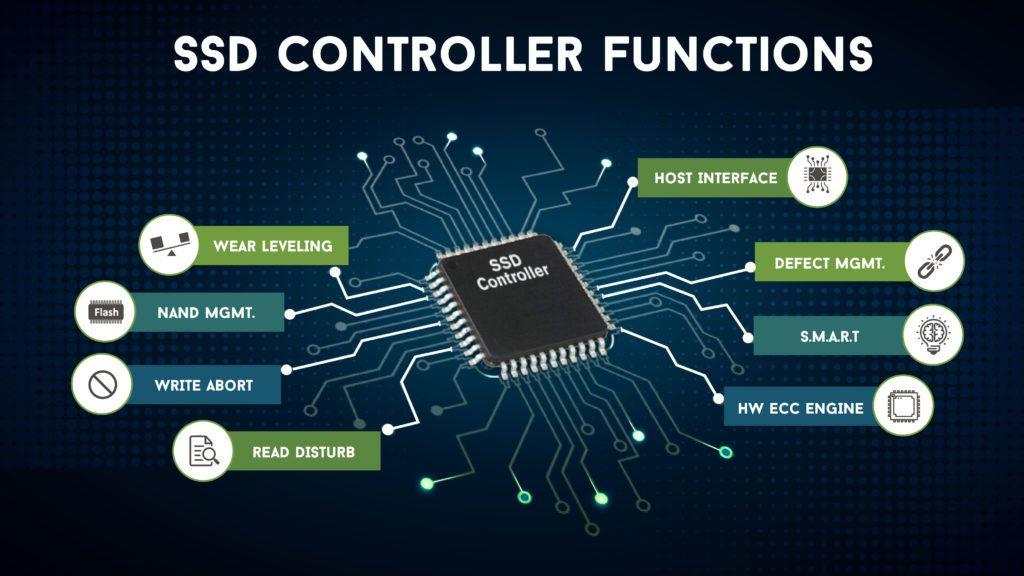

L'une des façons dont Mémoire NAND est devenu le moins cher de tout cela parce qu'il nécessite que la correction d'erreur soit effectuée à partir d'un élément extérieur à la puce NAND elle-même; Dans le cas des SSD, l'ECC est effectué sur le contrôleur .

Comment l'ECC fonctionne sur un contrôleur SSD

Cette même correction d'erreur aide également à corriger les erreurs de bits dues à porter sur le Mémoire cellules elles-mêmes . L'attrition peut provoquer le «blocage» des bits dans un état ou un autre (connu sous le nom d'erreur «matérielle», ou erreur matérielle) et peut augmenter la fréquence des erreurs «logicielles».

Bien que ce ne soit pas un concept trop large, la résistance de la mémoire flash est une mesure du nombre de cycles d'effacement / d'écriture qu'un bloc flash peut supporter avant que des erreurs «matérielles» ne commencent à apparaître. Très souvent, ces échecs ne sont que dans des bits individuels, et il est très rare que le bloc entier échoue. Avec un nombre d'effacement / d'écriture suffisamment élevé, le taux d'erreur «souple» augmente également en raison d'un certain nombre d'autres mécanismes dans le SSD lui-même.

If ECC peuvent être d'utiliser pour corriger ces erreurs «hard» et les erreurs «soft» n'augmentent pas, alors la durée de vie de l'ensemble du bloc est fortement allongée, bien au-delà de la résistance spécifiée par le constructeur.

Prenons un exemple: disons qu'une puce NAND inutilisée a suffisamment d'erreurs «douces» pour nécessiter 8 bits d'ECC, c'est-à-dire que chaque page lue peut avoir jusqu'à 8 bits qui ont été corrompus aléatoirement (généralement en raison du bruit électrique que nous parlaient). en premier). L'ECC utilisé dans cette puce peut corriger les erreurs de 12 bits, de sorte que l'ECC n'a pas pu résoudre ce problème nous devrions trouver 8 erreurs «douces» liées au bruit électrique plus 5 autres erreurs «douces» dues à l'usure.

Désormais, les fabricants de mémoire flash garantissent que la première de ces 5 défaillances se produira quelque temps après la spécification de résistance du SSD. Cela signifie qu'aucun bit n'échouera en raison de l'usure jusqu'à ce que les cycles d'effacement / d'écriture spécifiés par le fabricant soient dépassés. Maintenant, gardez à l'esprit que les spécifications ne sont pas assez précises pour prédire quand le bit suivant échouera, et cela peut prendre plusieurs milliers de cycles d'effacement / d'écriture au-dessus de la spécification pour que cela se produise; rappelez-vous que le fabricant garantit que cela ne se produira pas avant X cycles, mais pas quand cela se produira une fois qu'ils seront dépassés.

Cela signifie que cela peut prendre beaucoup de temps avant un bloc devient tellement corrompu qu'il doit être retiré du service (et aussi pour cela, le SSD a généralement des blocs «supplémentaires» pour remplacer les blocs corrompus), ce qui signifie que le résistance de la correction d'erreur bloc peut être plusieurs fois supérieure à la résistance spécifiée, selon le nombre d'erreurs excédentaires que l'ECC est conçu pour corriger.

Quel impact le code de correction d'erreur a-t-il sur un SSD?

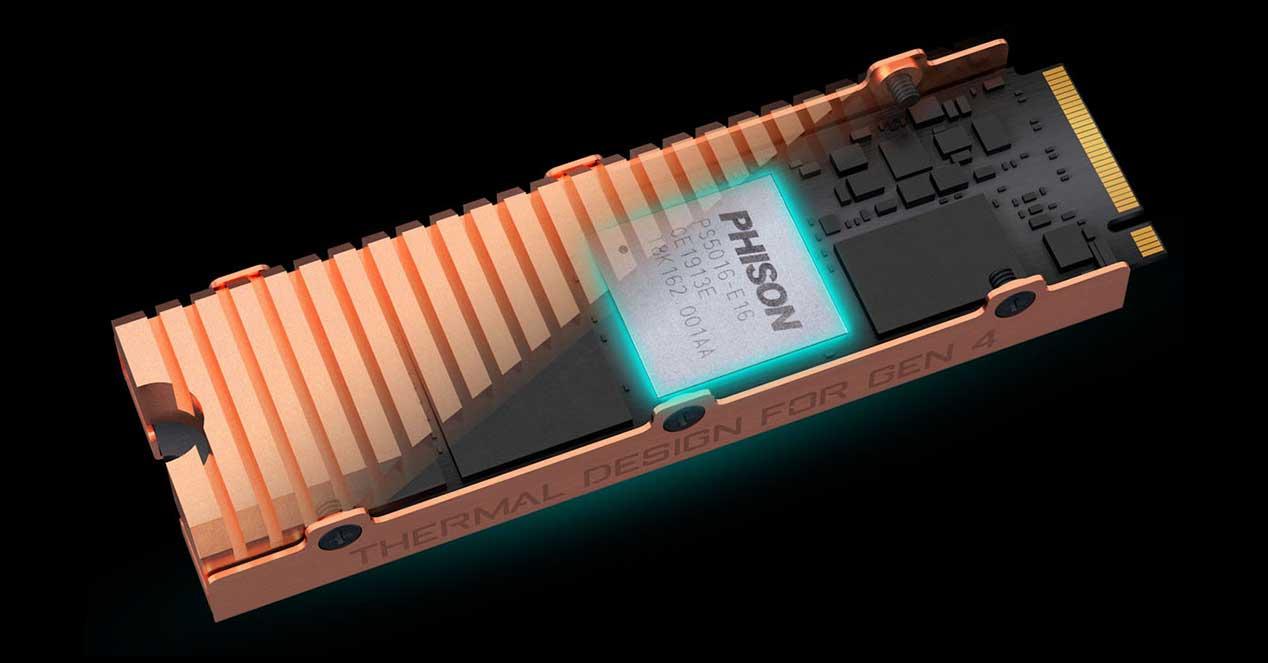

Comme nous l'avons expliqué précédemment, la mémoire flash est si bon marché car elle n'inclut pas l'ECC dans les puces elles-mêmes, mais est intégrée à un autre matériel externe à celles-ci, et comme vous le supposerez, cela a un prix. Un ECC plus sophistiqué nécessite plus de puissance de traitement sur le contrôleur et peut être plus lent si les algorithmes ne sont pas très modernes. En outre, le nombre d'erreurs pouvant être corrigées dépendra de la taille du secteur de mémoire corrigé, de sorte qu'un contrôleur SSD avec un algorithme ECC sophistiqué est susceptible d'utiliser beaucoup de ressources, réduire SSD global performant . Ces améliorations font également le contrôleur plus cher .

Les algorithmes ECC ont leur propre état mathématique en fonction du contrôleur (en d'autres termes, il n'y a pas de standard), et même les encodages ECC les plus basiques (Reed-Solomon et LDPC) sont assez compliqués à comprendre. Quand quelqu'un parle de la limite de Shannon (le nombre maximum de bits qui peuvent être corrigés), c'est une quantité qui, comme vous ne le savez pas du fabricant dans les spécifications techniques, est extrêmement difficile à calculer.

Tenez-vous-y: plus de bits de correction conduisent à une durée de vie plus longue pour le SSD, mais cela a également un impact sur les performances, voire le prix du produit, en nécessitant un contrôleur plus puissant.