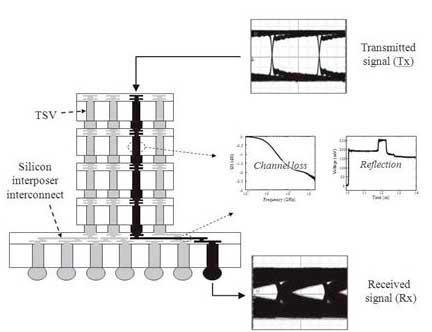

Aus HBM-Erinnerungen Durch 3D NAND Chips Es gibt viele Chips auf dem Hardwaremarkt, die mit dem sogenannten TSV hergestellt werden. Diese Akronyme bedeuten „Through Silicon Vias“ und werden übersetzt als über Silizium durch die Tatsache, dass sie die Chips vertikal kreuzen und eine vertikale Interkommunikation zwischen ihnen ermöglichen. In diesem Artikel werden wir Ihnen sagen, was sie sind, wie sie funktionieren und wofür sie sind.

In der Hardwarewelt wird häufig über Begriffe gesprochen, die mit Geschwindigkeitsraten zu tun haben, sei es die Bandbreite eines Speichers, die Taktzyklen eines Prozessors, wie oft ein Prozessor eine Art Berechnung pro Sekunde durchführt usw. , aber sehr selten fragen wir uns, wie die Chips miteinander kommunizieren und ob dies wichtig ist.

![]()

In diesem Artikel werden wir über eine Technologie namens TSV sprechen, die zur Kommunikation von Chips verwendet wird, unabhängig davon, um welche es sich handelt.

Was sind Silizium- oder TSV-Pfade?

Wenn wir uns die meisten Motherboards ansehen, sehen wir zwei Dinge: Das erste ist, dass die meisten Verbindungen zwischen Chips horizontal sind, was bedeutet, dass die Pfade auf der Platine, die das Signal zwischen Chips senden, horizontal kommunizieren.

Dann haben wir den Fall von CPUs, die auf einem Interposer platziert sind, den wir Socket nennen und in dem die Prozessoren vertikal an ihnen angeschlossen sind.

Im Allgemeinen stellen wir jedoch in 99% der Fälle fest, dass normalerweise keine Chips vertikal miteinander verbunden sind, und obwohl sich das Design von Chips und Prozessoren in diese Richtung entwickelt und es bereits einige Beispiele für diesen Typ auf dem Markt gibt . Aber wie machen wir das, um zwei oder mehr Chips vertikal miteinander zu kommunizieren?

Nun, genau dies geschieht mit sogenannten Pfaden durch Silizium, die die verschiedenen Chips oder Schichten desselben Chips, aus denen der Stapel besteht, vertikal kreuzen. Deshalb werden sie als "durch" Silizium bezeichnet, weil sie buchstäblich durchlaufen.

Die Anwendungen und Vorteile der Verwendung von TSVs

Eine der Anwendungen von TSV besteht darin, dass komplexe Prozessoren, die aus verschiedenen Teilen bestehen, auf mehreren verschiedenen Chips getrennt werden können, mit dem zusätzlichen Vorteil, dass die vertikale Konnektivität eine größere Anzahl von Verbindungen ermöglicht, wodurch höhere Bandbreiten erreicht werden können, ohne dass ein Very erforderlich ist Hohe Taktfrequenz, die den Stromverbrauch während der Datenübertragung erhöht.

In Zukunft werden wir beispielsweise CPUs und GPUs sehen, bei denen der Cache der letzten Ebene außerhalb des Chips liegt, mit derselben Bandbreite, aber einer um ein Vielfaches höheren Speicherkapazität, was die Leistung erheblich steigern wird. Wir haben auch das Beispiel der Intel Foveros, der TSV verwendet, um die beiden Teile des Lakefield SoC, das Compute Chiplet, mit dem Basis-Die zu kommunizieren, in dem sich die System-E / A befindet.

Der Grund für die Aufteilung eines Prozessors in verschiedene Teile liegt in der Tatsache, dass mit zunehmender Größe eines Chips die Wahrscheinlichkeit eines Fehlers in der Schaltung immer größer wird und daher die Anzahl der guten Chips ohne Fehler, die verwendet werden können, geringer ist das muss gut die Kosten für diejenigen bezahlen, die versagt haben; Dies bedeutet, dass das Reduzieren der Größe der Chips theoretisch die Gesamtkosten reduziert, obwohl wir später sehen werden, dass dies nicht vollständig der Fall ist.

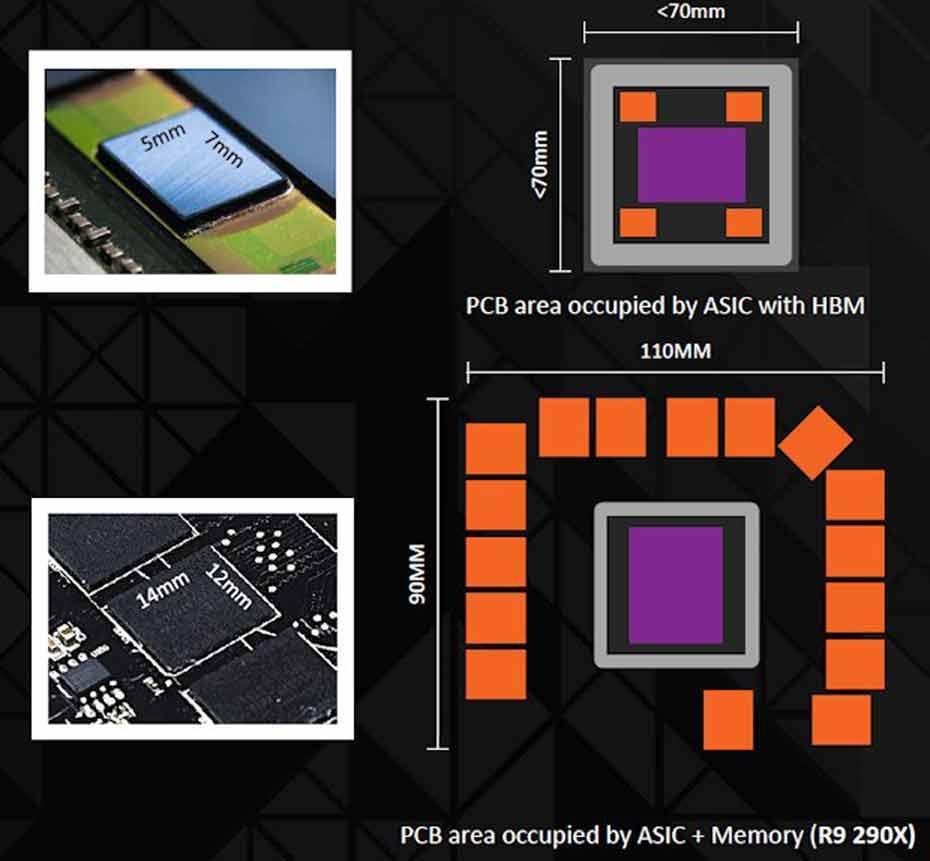

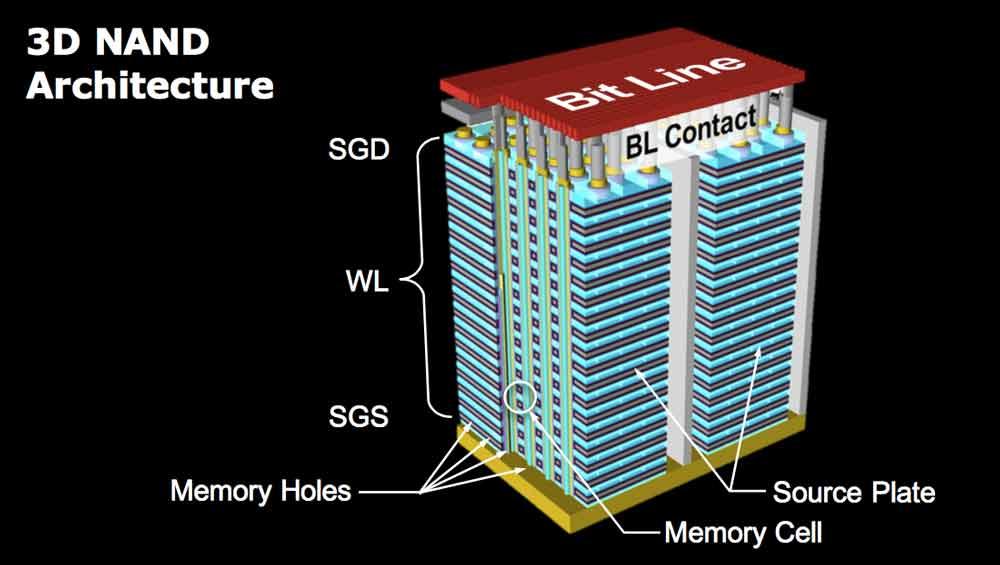

Die zweite Anwendung hat mit dem belegten Raum zu tun; Die Tatsache, dass mehrere Chips vertikal gestapelt werden können, reduziert die Fläche, die sie einnehmen, erheblich, da sie nicht auf der Platine verteilt sind. Das bekannteste Beispiel hierfür ist der HBM-Speicher, der für bestimmte Grafikprozessoren als VRAM verwendet wird. Wir haben jedoch andere Beispiele wie z wie SamsungV-NAND-Speicher, der mehrere NAND-Flash-Speicherchips übereinander stapelt.

Andere weniger bekannte Optionen sind die Kombination aus Logik und Speicher, bei der der Speicher auf einem Prozessor platziert wird. Das bekannteste Beispiel ist der Wide I / O-Speicher, ein Speichertyp, der vor einigen Jahren in Smartphones vorkam und bestand eines Speichers auf dem SoC, der über Silizium miteinander verbunden ist.

Warum ist die Einführung von Siliziumwegen so langsam?

Der TSV weist mehrere inhärente Probleme auf, was dazu geführt hat, dass er, obwohl er seit Jahrzehnten eine vielversprechende Technologie auf dem Papier ist, nicht ganz auf dem Vormarsch ist und eine Möglichkeit bleibt, Chips für sehr kleine Märkte mit hohen Margen herzustellen.

- Ihr erstes Problem ist, dass es sich um eine extrem teure Technologie handelt, deren Implementierung tiefgreifende Änderungen in den Fertigungslinien vieler Unternehmen erfordert, die seit Jahren Chips ohne TSV herstellen, und für viele Anwendungen hat sich gezeigt, dass das herkömmliche Herstellungsverfahren gut genug ist. .

- Das zweite Problem besteht darin, dass, wenn ein Teil der vertikalen Struktur vollständig ausfällt, die gesamte Struktur weggeworfen werden muss, was die Herstellung von über TSV miteinander verbundenen Systemen erheblich verteuert. Das Beispiel des HBM-Speichers ist dabei von Bedeutung, seine Kosten sind so hoch, dass er als Speicher für den Verbrauchermarkt nicht geeignet ist.

- Das dritte Problem ist das thermische Ersticken. Die Chips erreichen die Taktraten, die sie unter bestimmten Temperaturbedingungen erreichen. Diese sind betroffen, wenn sich in der Nähe ein anderer Chip befindet, der ebenfalls Wärme abgibt. Wir können zum Beispiel zwei Prozessoren haben, die separat jeweils 1 GHz erreichen, aber zusammen vertikal in einer TSV-Struktur angeordnet sind und aufgrund von Temperaturproblemen jeweils nur 0.8 GHz erreichen.

Der dritte Punkt ist derjenige, den Ingenieure heute am meisten beunruhigen, und es werden Kühlmechanismen entwickelt, um die Chips, aus denen der Stapel besteht, so kalt wie möglich zu halten, um Probleme mit dem thermischen Ertrinken zu vermeiden.