Ein guter Teil der Leistung unserer PCs basiert auf der Arbeitsteilung, bei der sich mehrere Elemente die Ausführung eines Teils des Codes teilen, um damit zu arbeiten. Aber manchmal gibt es Konflikte beim Zugriff auf Daten und Anweisungen, die zu einem Leistungsproblem werden. Eine Möglichkeit, dies zu beheben, ist der Transaktionsspeicher.

Eines der größten Probleme mit dem Multicore CPU Systeme, die unsere PCs verwenden, basieren auf dem Von-Neumann-Modell, dh es gibt nur einen gemeinsamen Speicher. Mit zunehmender Anzahl von Ausführungseinheiten, Kernen, Threads und anderen Elementen, die in einer CPU parallel arbeiten, steigt. Zwischen ihnen entstehen immer mehr Konflikte. Nicht nur beim Zugriff auf die Daten, sondern auch bei den in den verschiedenen Speicheradressen enthaltenen Informationen und damit dem Wert der von den Programmen verwendeten Variablen. Es gibt viele Methoden, um diese Konflikte zu vermeiden, eine davon ist der Transaktionsspeicher, den wir in diesem Artikel beschreiben werden.

Eine Einführung in das Problem

Beim Schreiben eines Programms wird es in eine Reihe von Befehlen kodiert, die anscheinend sequentiell ausgeführt werden. Aber schon bei der Parallelität von Anweisungen mit einem einzigen Kernel mitten in der Ausführung können verschiedene Ausführungseinheiten eintreten. Dazu müssen wir berücksichtigen, dass die ungeordnete Ausführung die Komplexität erhöht, dass der Zugriff auf Speicher und Daten zur Laufzeit ungeordnet erfolgt.

Wenn es eine große Anzahl von Anforderungen gibt, führt dies zu einem Konflikt um den Zugriff auf denselben Speicher. Dies führt dazu, dass Anforderungen immer länger verzögert werden, was die Speicherlatenz mit der CPU bei bestimmten Befehlen erhöht und die Bandbreite beeinträchtigt. Dafür gibt es Mechanismen, die diese Konflikte beim Speicherzugriff weitestgehend vermeiden, so dass die Prozesse aus einem geordneten Speicher auf den Speicher zugreifen. Dies vermeidet Konflikte beim Ändern der Daten in ihrer Hierarchie und reduziert Konfliktprobleme und folglich die Zugriffslatenz.

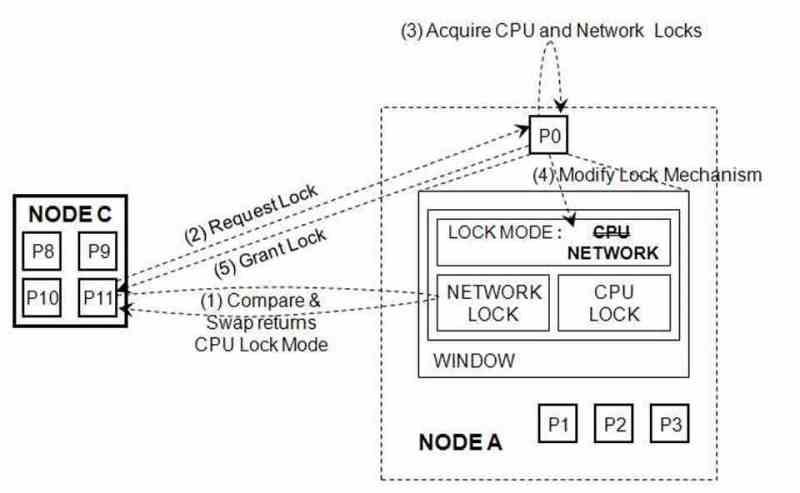

Der einfachste Weg, dies zu erreichen, sind Sperren, die Abschnitte des Codes sind, in denen wir markieren, dass sie nicht gleichzeitig von verschiedenen Threads der CPU ausgeführt werden müssen. Das heißt, nur ein Kern davon kann für diesen Teil des Codes verantwortlich sein. Wir haben also den Rest der Kerne gesperrt und der Rest kann nur dann in die Ausführung eintreten, wenn der Befehl erreicht ist, der die Sperre beendet. Was passiert, wenn der Teil des Codes, der auf alle Kerne außer einem isoliert ist, abgeschlossen ist.

Was ist Transaktionsgedächtnis?

Eine Methode zur Vermeidung der im vorherigen Abschnitt beschriebenen Probleme besteht darin, Transaktionsspeicher zu verwenden. Das ist keine Art von Speicher oder Speicher, also sprechen wir nicht von einer reinen Hardware. Sein Ursprung liegt in den Transaktionen der Datenbanken, es ist eine Art von Anweisungen, die in den Load-Store-Einheiten ausgeführt werden.

Das Transaktionssystem in einem Prozessor funktioniert wie folgt:

- Eine Kopie des Teils des Speichers, auf den mehrere Kerne zugreifen möchten, wird erstellt, eine für jede Instanz.

- Jede Instanz ändert ihre private Kopie unabhängig von den übrigen privaten Kopien.

- Wenn Daten in einer Privatkopie und nicht in den übrigen geändert wurden, wird die Änderung auch in die restlichen Privatkopien kopiert.

- Wenn zwei Instanzen gleichzeitig eine Änderung an denselben Daten vornehmen und dadurch eine Inkonsistenz in den Daten entsteht, werden beide Privatkopien gelöscht. und die privaten Kopien des Rests werden kopiert

Der vierte Punkt ist wichtig, da an diesem Teil deutlich wird, dass dieser Teil des Codes serialisiert werden muss. Dies bedeutet, dass die restlichen Instanzen ihre privaten Kopien nicht mehr ändern und die Änderungen nur von einer der Instanzen vorgenommen werden. Am Ende werden die Änderungen auf die restlichen privaten Kopien kopiert. Wenn der als transaktional gekennzeichnete Teil des Codes bereits ausgeführt wurde und alle privaten Kopien die gleichen Informationen enthalten, wird das Ergebnis in die entsprechenden Cache-Zeilen und Speicheradressen kopiert.

Transaktionsspeichersysteme, die Intel TSX

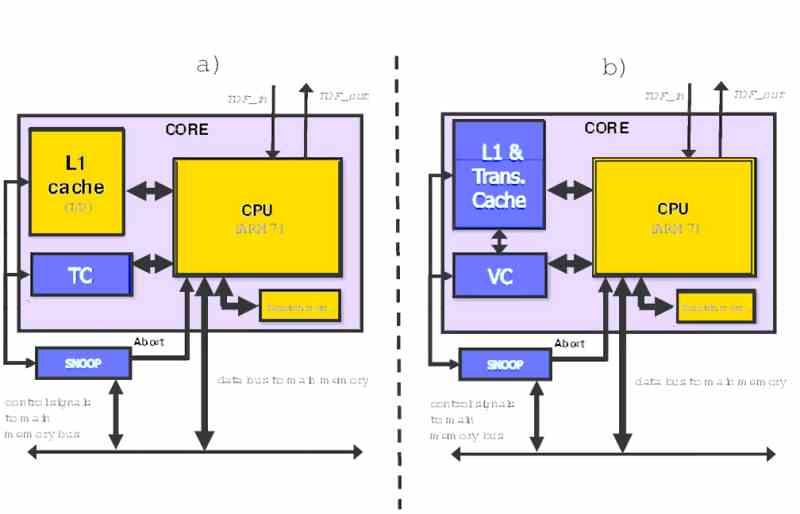

Das Akronym TSX, Erweiterungen für die Transaktionssynchronisierung, bezieht sich auf eine Reihe zusätzlicher Anweisungen für die x86-ISA, die dazu gedacht sind, Transaktionsspeicherunterstützung zu Intel CPUs. Daher ist es eine Reihe von Anweisungen und Mechanismen, die mit ihnen verbunden sind, die es ermöglichen, bestimmte Abschnitte des Codes als transaktional abzugrenzen und die Intel-CPU den Prozess auszuführen, den wir im vorherigen Prozess besprochen haben. Aber in diesem Fall ist die Intel-Implementierung etwas komplexer. Denn wie wir bereits gesehen haben, wird bei einem Konflikt zwischen zwei Daten der gesamte Vorgang von einer der laufenden Instanzen abgebrochen.

Seine Implementierung in Hardware wird durch Hinzufügen eines neuen Cache-Typs erreicht, der als Transaktionscache bezeichnet wird und in dem die verschiedenen Operationen an den verschiedenen Daten ausgeführt werden. Denken Sie daran, dass der Transaktionsspeicher versucht, Konflikte beim Zugriff auf den Speicher zu reduzieren. Obwohl die Caches eine größere Anzahl von Anfragen unterstützen als die RAM im Allgemeinen sind diese ebenfalls begrenzt und insbesondere auf den von den Kernen am weitesten entfernten Ebenen. All dies wird mit der Verwendung von internen Speichern und privaten Registern kombiniert, die als Unterstützung für die von den verschiedenen Kernen ausgeführten privaten Kopien dienen.

Die Intel TSX-Befehle sind kein komplexer Satz, wir haben zum einen den XBEGIN-Befehl, der uns markiert, wenn ein transaktionaler Speicherabschnitt beginnt, den XEND-Befehl, der das Ende markiert, und den XABORT, der dazu dient, einen Prozessausstieg zu markieren wenn eine Ausnahmesituation eintritt.

Das Ende der Intel TSX-Anweisungen?

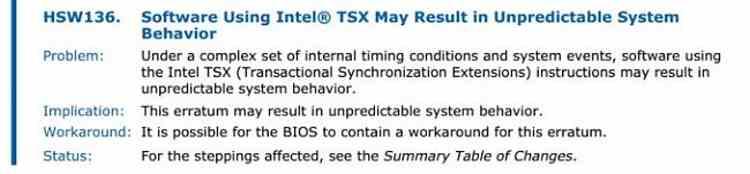

Heutige CPU-Steuereinheiten sind eigentlich ausgewachsene Mikrocontroller, das heißt, die Art und Weise, wie sie Anweisungen dekodiert und die Liste der Anweisungen aktualisiert werden können. Intel hat die erste Implementierung auf der Haswell-Architektur vorgenommen und ist bisher innerhalb der Intel-CPUs geblieben. Seit kurzem wurde es per Firmware auf Intels eigenen Kernen der sechsten, siebten und achten Generation deaktiviert.

Von Zeit zu Zeit führt Intel Remote-Updates seiner CPUs durch, die ohne unser Wissen über die Intel Management Engine, die wir in unserem PC haben, durchgeführt werden. Sie sind normalerweise nicht üblich, können jedoch Optimierungen bei der Ausführung bestimmter Anweisungen oder sogar die Eliminierung der Unterstützung für andere umfassen. Die Eliminierung des Intel TSX im Intel Core ist darauf zurückzuführen, dass die neuesten Änderungen des internen Mikrocodes der Steuereinheit einen Konflikt in der Bedienung der Software implizieren, was bedeutet, dass die CPU nicht so funktioniert, wie sie sollte.

Aber der wahre Grund ist, dass die Intel TSX die Ausführung von Schadcode unter dem Radar klassischer Sicherheitssysteme ermöglicht, insbesondere solcher, die das Betriebssystem betreffen. Da die privaten Kopien nicht der Umgebung des Benutzers oder dem Betriebssystem entsprechen. Es ist also immer noch ein ähnliches Problem wie bei der spekulativen Ausführung.