Bisher ist noch kein Chip auf dem Markt erschienen, der auf dem N3- oder 3-nm-Knoten von TSMC hergestellt wurde. Die neuesten Nachrichten sind jedoch wirklich schlecht, da sich ein Produkt im Laufe der Zeit verbessert hat und Technologie nach Technologie für immer stagniert hätte. Ist SRAM endgültig stagniert?

Das oft missverstandene Gesetz von Moore hat in den letzten Jahren mehrere Ankündigungen seines Endes erlebt. Mit der jüngsten Ankündigung von TSMC bezüglich seines 3-nm-Knotens könnte diese Behauptung jedoch wahr werden. Zumindest angesichts einer Art von Transistorkombination, die in allen Arten von Prozessoren weit verbreitet ist, und dies wird die Chipentwicklung in den folgenden Jahren bremsen.

Schlechte Nachrichten: Sie können die Größe des SRAM nicht mehr reduzieren

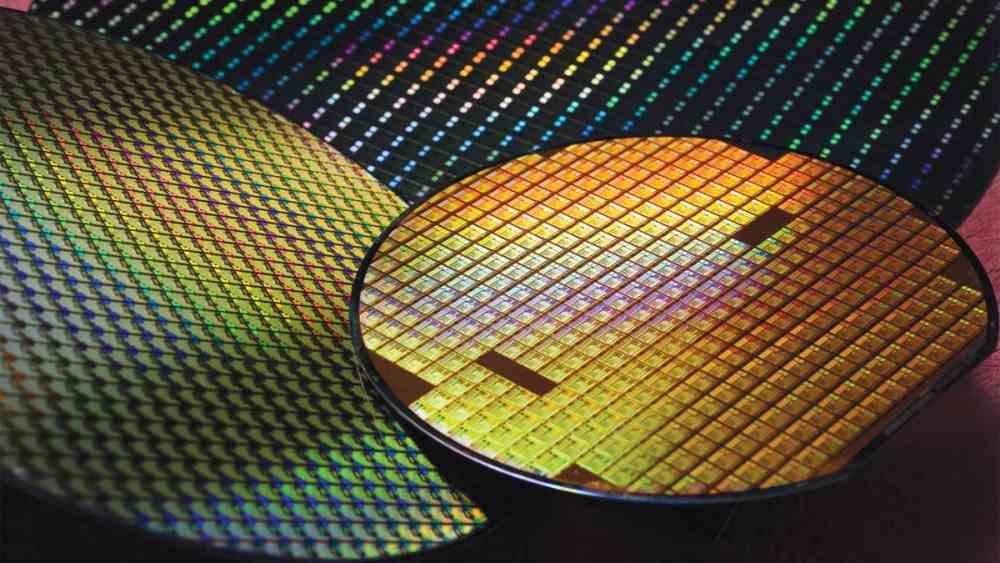

Wie üblich stellen wir bei jedem neuen Herstellungsknoten fest, dass die Transistoren, ob Logik oder Speicher, auf eine kleinere Größe skaliert werden. Im Fall von Speicher bedeutet dies größere interne Speicher oder einfach die Möglichkeit, mehr davon auf demselben Platz unterzubringen. Der 3-nm-Knoten von TSMC bringt jedoch einige sehr schlechte Nachrichten, wenn es darum geht, die Größe des SRAM von dem derzeit verwendeten 5-nm-Knoten zu skalieren.

Nun, während einer Konferenz bei der 68. Ausgabe des IEEE International Electron Devices Meeting (IEDM), wo sich mehr als 1000 Ingenieure aus der Industrie versammelt haben, und damit die Leute, die die Hardware entwickeln, die Sie in Ihren PCs verwenden, kurz und mittel langfristige Entwicklungen der Branche werden diskutiert. Die Leute von TSMC haben über ihren 3-nm-Knoten gesprochen, der von zukünftigen Ryzen-Prozessoren und auch von Ryzen verwendet wird Apple, sowie GeForce- und Radeon-Grafikkarten der nächsten Generation. Was ist passiert? Die taiwanesische Gießerei hat sehr schlechte Nachrichten veröffentlicht.

Um zu verstehen, was passiert, müssen wir davon ausgehen, dass TSMC zwei Varianten seines 3-nm-Knotens hat.

- Der erste namens N3B kann SRAM mit einer Dichte von 0.0199 Quadratmikrometern pro Bit herstellen, was einer Reduzierung von nur 5 % gegenüber dem 5-nm-Knoten entspricht.

- Bei der anderen Variante N3E gibt es keinerlei Skalierung. Das bedeutet, dass der vom SRAM im Prozessor belegte Bereich zunimmt.

Es ist ein wesentliches Stück

Aufgrund der Tatsache, dass SRAM zum Aufbau interner Speicher verwendet wird, die für das Funktionieren von Prozessoren unerlässlich sind, wie z. B. Register und Caches. Daher ist es ein wesentliches Element, und diese Einschränkung könnte viele der Fortschritte nicht gefährden, die für zukünftige Prozessorgenerationen erwartet werden, bei denen die Tendenz besteht, den Speicher näher an den Prozessor zu bringen, um das Latenzproblem zu verringern. und Energieverbrauch beim Verschieben der Daten.

Somit müssen wir zum Problem der Datenbewegung und der Energiekosten das der Speicherung hinzufügen. Nicht zugewandt RAM Speicher, da sie DRAM-Speicher verwenden, aber innerhalb des Prozessors. Mit anderen Worten, die Größe der Caches wird nicht zunehmen und das Hinzufügen neuer Kerne wird im Vergleich zu den Fortschritten, die wir in den letzten Jahren gemacht haben, geringer als erwartet sein, genau wegen dieser Einschränkung bei der Skalierung des SRAM-Speichers von einem Knoten auf einen Ein weiterer.

Ist es ein einzigartiges TSMC-Problem?

Da Intel kürzlich die Entscheidung getroffen hat, Chiphersteller nicht nur für ihre Produkte, sondern auch für Dritte zu werden, sind sie in einen harten Wettbewerb mit der taiwanesischen Gießerei um andere zur Herstellung ihrer Chips eingetreten. Im Moment kennen wir die Dichte des SRAM im Intel 4-Knoten nicht, der zeitlich mit den auf den Markt kommenden Teilen zusammenfallen wird. Obwohl alles darauf hindeutet, dass das Verfahren des amerikanischen Herstellers in Sachen Dichte etwas unter SRAM liegt.

All dies deutet auf jeden Fall darauf hin, dass die Entwicklung von 3DIC-Speicherkonfigurationen aus mehreren gestapelten Chips durchgesetzt wurde AMD mit dem Ryzen X3D und dem V-Cache wird in Zukunft eine häufigere Lösung sein, als wir erwartet haben und kein einfaches Experiment, da es die einzige Möglichkeit sein wird, einen Last-Level-Cache mit genügend Kapazität zu implementieren, damit die SRAM-Skalierungsbeschränkung funktioniert nicht zu Engpässen führen. Das andere Mittel besteht darin, größere Chips zu bauen, aber mit steigenden Kosten ist es völlig klar, dass Hardware, wenn sie jetzt teuer ist, Gefahr läuft, ein Luxusartikel zu werden.