In einer Konferenz, die Intel hat in China gegeben, der Präsident des Forschungszentrums, das das Unternehmen in diesem Land hat, hat über die Ziele gesprochen, die sie für 2030 haben und die sich zusammenfassen lassen, indem HP-Chips immer kleiner werden und immer weniger verbrauchen. Was sich in einer größeren Anzahl von Transistoren und einer höheren Energieeffizienz niederschlägt . Wie wollen sie das erreichen?

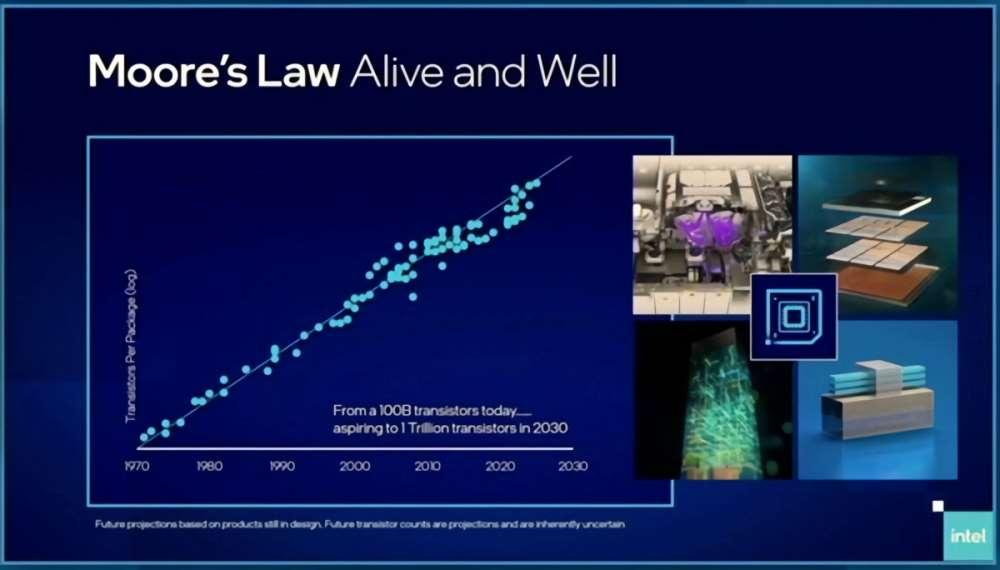

Das Mooresche Gesetz, das vom Gründer von Intel geprägt wurde und auch nicht als Gesetz, sondern als Beobachtung bezeichnet werden kann, wird oft falsch interpretiert, da die Konzepte darüber oft verwechselt werden. Auf jeden Fall muss klargestellt werden, dass es sich nicht um die Sparsamkeit der Chips oder deren Leistung handelt, sondern um die sich immer wieder verdoppelnde Dichte der Transistoren auf einem gegebenen Raum. Obwohl sich dies im Laufe der Zeit verlangsamt hat, ist die Realität, dass es heute noch gültig ist.

Eine Billion Transistorchips bis 2030 von Intel

Für diejenigen von uns, die den Fortschritt der Welt der Chips, also der Halbleiter, verfolgen, ist uns heute sehr klar, dass die Zukunft, um die Dichte von Transistoren von Zeit zu Zeit verdoppeln zu können, den Einsatz erfordert von neuen Fertigungstechniken. und Design, insbesondere Konzepte wie zersplitterte Chips und die Verwendung dreidimensionaler Strukturen, dh das Stapeln von Chips übereinander und all dies, um Chips zu machen wird bis zu 10 Mal effizienter sein und bis zu einer Billion im Inneren beherbergen. von Transistoren.

Derzeit ist der komplexeste Chip, der in PCs verwendet wird NVIDIA's AD102, das wir für das zentrale halten GPU der RTX 4090, die eine Dichte von 7.6 % im Vergleich zu diesem Ziel hat, also sprechen wir von einer ziemlich langen Zeit für Intel, um dieses Ziel zu erreichen, außerdem haben sie erwogen, es bis 2030 zu erreichen, obwohl wir es nicht tun wissen, ob sie dies in ihren Core-CPUs oder umgekehrt in ihren ARC-GPUs tun werden. Vergessen wir nicht, dass die sogenannten desintegrierten Mikroprozessoren oder Chiplets es ermöglichen, die Gittergrenze des Wafers zu durchbrechen und Zusammensetzungen mit einer größeren Anzahl von Transistoren als in einem monolithischen Chip zu erstellen.

In jedem Fall müssen wir bedenken, dass sich das Panorama nach dem Versand der einteiligen Chips vollständig geändert hat, da dies die offensichtliche Verwendung kleinerer Chips bedeutet, was auch aufgrund der Kostensteigerung bei jedem neuen verfolgt wird Knotenpunkt der Chipherstellung.

Eine Verbesserung der Energieeffizienz um eine Größenordnung

Wenn wir bereits über Energieeffizienz sprechen, müssen wir berücksichtigen, dass diese Worte, obwohl sie ein lobenswertes Ziel für Dinge wie die Reduzierung des COXNUMX-Fußabdrucks sind. Wir können nicht vergessen, dass wir nicht wissen, mit welcher Leistung sie diesen Parameter und die Art der Hardware messen wollen, sowie die Leistungstests, die sie als Referenz verwenden möchten, oder, falls dies heute nicht der Fall ist, Parameter wie das Haus der Anweisungen pro Sekunde, Fließkommazahl usw.

Es ist ein Ziel, das nicht leicht zu erreichen sein wird und das die Implementierung mehrerer Technologien erfordern wird, von denen sich viele noch in der Entwicklung befinden und andere bald eingesetzt werden. Wir sprechen über Dinge wie Transistoren vom RibbonFET-Typ für Dichten von 2 Nanometern oder weniger, Power VIA-Stromversorgungen, die Verwendung fortschrittlicher Lithografiesysteme, die derzeit noch unbekannt sind, und neue Chip-Packaging-Systeme ähnlich Foveros.