Die Zen 3-Architektur, die von der AMD Ryzen 5000 ist sowohl auf dem Desktop als auch in einigen Prozessoren der Notebook-Reihe derzeit der leistungsstärkste und fortschrittlichste CPU Architektur auf dem Markt. Aber welche Geheimnisse verbirgt sich darin, um diese Leistung zu erzielen?

Unabhängig davon, ob es sich um eine Chiplet-basierte CPU oder einen monolithischen Prozessor handelt, sind die Änderungen, die wir beschreiben werden, für alle AMD-Prozessoren, die auf Zen 3 basieren, allgemein.

Die Kerne der AMD Zen 3-Architektur

Um den Grund für die Leistungsänderungen in Bezug auf Zen 2 im Vergleich zu Zen 3 zu verstehen, müssen wir im Voraus verstehen, dass der Anstieg des IPC um 19% darauf zurückzuführen ist, dass beide Prozessoren einem Test oder mehreren Leistungstests unterzogen wurden und ein Durchschnitt ermittelt wurde der Leistung beider Architekturen.

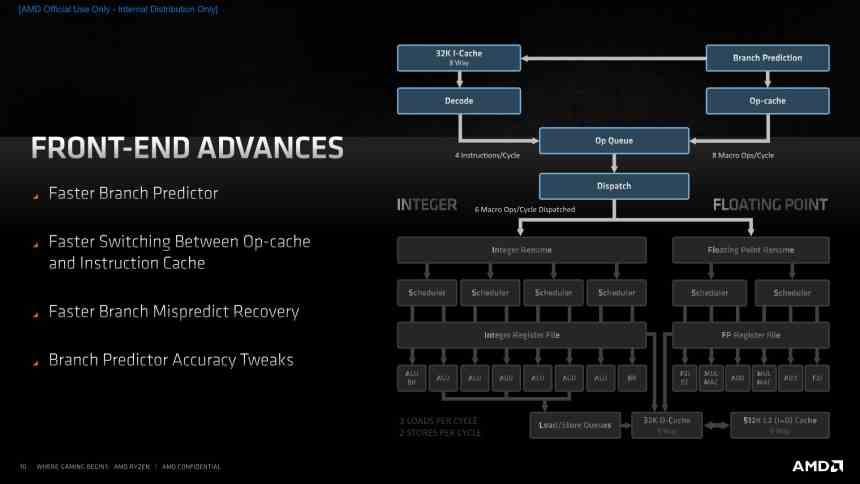

Auf den ersten Blick scheint Zen 3 eine leicht verbesserte Version von Zen 2 zu sein, da sich die Änderungen in Teilen des Prozessors befinden, die normalerweise unsichtbar sind, wenn es um die Leistung eines Prozessors geht. Diese Änderungen wurden insbesondere in der Steuereinheit oder vorgenommen Frontend des Prozessors.

Front-End-Verbesserungen für Zen 3-Kerne

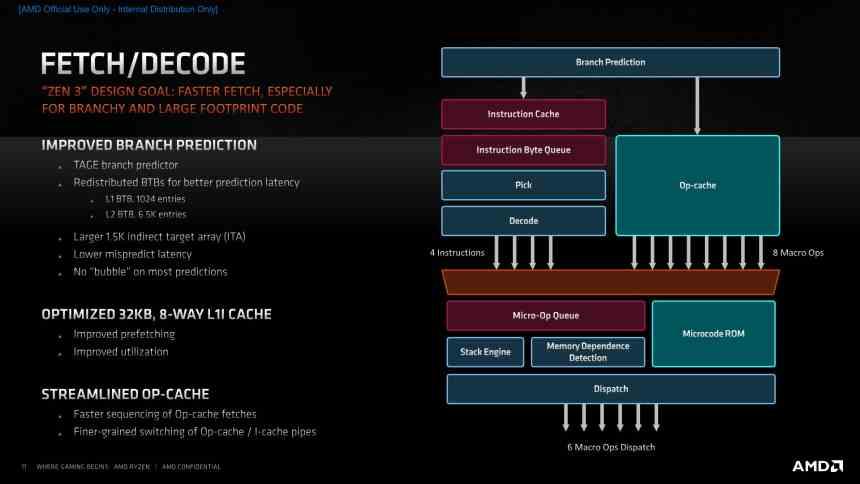

Unter den Neuheiten im Front-End des Prozessors ist die Komponente, die am meisten hervorgehoben wurde, die neue Sprungvorhersageeinheit Branch Predictor, die verbessert wurde, damit mehr Zweige pro Taktzyklus vorhergesagt werden können. Eine Reihe von Änderungen im Prozessor, z. B. eine Neugestaltung des BTB für den Verzweigungsvorhersagepuffer, der sich sowohl im L1-Cache befindet, da die Anzahl der Einträge von 512 auf 1024 gestiegen ist, als auch im L2-Cache von 7 KB abgenommen hat zu den 6.5K-Einträgen im Vergleich zu Zen 2.

Die neue Sprungvorhersageeinheit reduziert die Anzahl der Zyklen, die verloren gehen, wenn der Prozessor eine fehlgeschlagene Vorhersage macht, wodurch verhindert wird, dass Kerne viel länger sitzen, wenn die Sprungvorhersageeinheit ausfällt.

Andererseits. Wir können nicht vergessen, dass Prozessoren mit Zen 3-Architektur die x86-64-Register und -Anweisungen verwenden, was bedeutet, dass es sich um eine ISA vom Typ CISC handelt. Einer der Vorteile von CISC-Registern und Befehlssätzen besteht darin, dass sie mehrere einfache Befehle zu einem einzigen komplexen Befehl zusammenfassen, was beim Lesen von Code-Speicherplatz und Energie spart RAM.

Leider haben sie den Nachteil, dass sie sehr schwer zu segmentieren sind, um eine Pipeline zu erstellen. Deshalb müssen komplexe Anweisungen in einfachere interne Anweisungen dekodiert werden, die als Uops oder Mikrooperationen bezeichnet werden. Das heißt, es ist notwendig, die x86- zu dekodieren. Anleitung. 64 in einer einfacheren Art von Anweisungen, um sie einfacher segmentieren zu können und eine Pipeline implementieren zu können.

In RISC-Prozessoren ist die Anzahl der Bytes pro Befehl immer gleich, aber in einem ISA wie dem x86-64 haben sie unterschiedliche Größen, was es äußerst komplex macht, die verschiedenen Befehle und in einigen Befehlen speziell die Anzahl der Zyklen zu decodieren einen Befehl zu dekodieren ist zu hoch. Aus diesem Grund muss ein Cache-Typ implementiert werden, der eine schnellere Beschleunigungsarbeit ermöglicht, der sogenannte UOP-Cache, der auch den Energieverbrauch während der Befehlsdecodierungsphase reduziert.

Wir wissen nicht, inwieweit AMD den UOP-Cache und seine Kommunikation verbessert hat, aber es ist eines der Schlüsselelemente zur Verbesserung der Leistung in x86-64-Prozessoren und einer der Punkte, die AMD im Vergleich zu Zen verbessert hat 2.

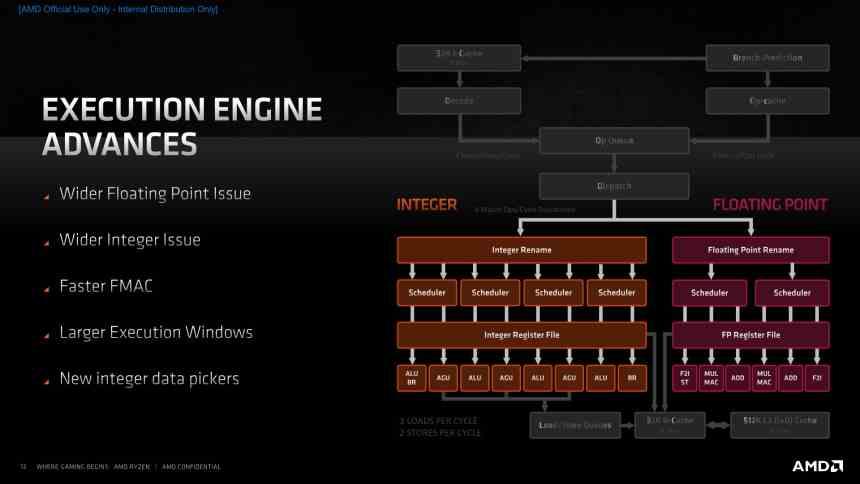

Ausführungseinheiten in Zen 3

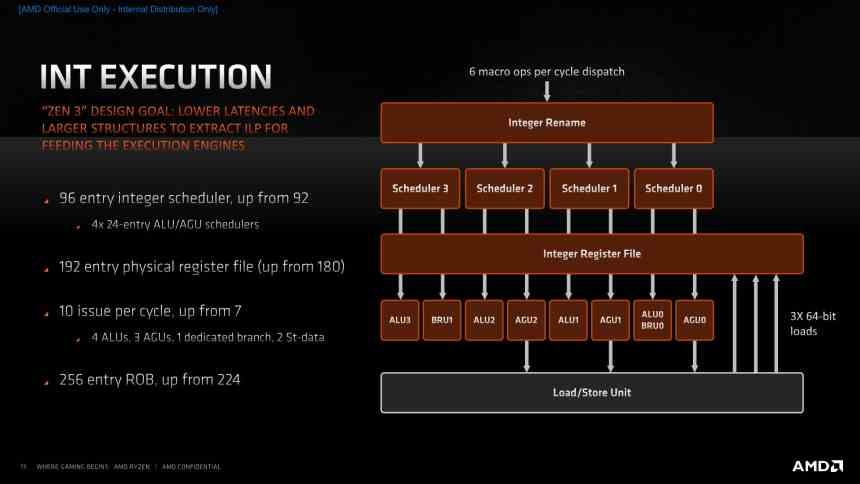

Wenn es um das Senden von Anweisungen geht, verfügt Zen 3 immer noch über eine Dispatch-Einheit, die 6 Macro-Ops pro Zyklus an die Ausführungseinheiten sendet, sodass der maximale CPI pro Kern bei 6 bleibt und sich theoretisch nicht erhöht hat. Kurioserweise kann das Front-End des Prozessors 8 Anweisungen gleichzeitig senden, was darauf hindeutet, dass in einer zukünftigen Iteration der Zen-Architektur eine Leistungssteigerung durch Erhöhung der Anzahl der Ausführungseinheiten zu sehen ist. aber in Zen 3 ist es gewohnt

Das Erhöhen der Anzahl von Ausführungseinheiten ist jedoch nicht die einzige Möglichkeit, die Anzahl von gleichzeitigen Befehlen pro Zyklus zu erhöhen, die ein Prozessor ausführen kann. Da eines der Probleme, mit denen Architekten konfrontiert sind, die für das Entwerfen eines Prozessors verantwortlich sind, die Menge an Ressourcen ist, die zum Erstellen der gesamten Architektur zur Verfügung stehen, führt dies häufig zu unterschiedlichen Anweisungen, die beim Ausführen denselben Pfad verwenden.

Wenn zwei Befehle, die parallel arbeiten, denselben Pfad verwenden, bis sie aufgelöst werden, tritt ein Konflikt auf, bei dem einer der Befehle die Ausführung des anderen verlangsamt, da sich ein Teil in der Pipeline befindet von anderen geteilt. Dies wirkt sich negativ auf die Anzahl der Anweisungen pro Zyklus und damit auf die Leistung des Prozessors aus.

Die Idee, neue Pfade hinzuzufügen, damit bei der Ausführung bestimmter Anweisungen keine Konflikte auftreten, ist wichtig, um den tatsächlichen IPC einer Architektur zu erhöhen. Dies ist der Fall bei Ganzzahleinheiten in Zen 3, bei denen die Anzahl der Pfade, denen Anweisungen folgen können, die die Ganzzahleinheit von 7 bis 10 verwenden, erweitert wurde, um Konflikte zwischen Befehlen zu vermeiden.

Andere mögliche Änderungen sind die Tatsache, dass der interne Betrieb bestimmter Befehle neu gestaltet wird, sodass weniger Zyklen für die Ausführung erforderlich sind, wie dies beim FMAC-Befehl in Gleitkommaeinheiten der Fall ist, der von einer Latenz von 5 Taktzyklen auf nur 4 Taktzyklen übergegangen ist Taktzyklen.

Der andere Einheitentyp, den AMD in Zen 3 verbessert hat, ist das sogenannte Laden / Speichern, das für das Laden und Speichern von Daten vom und zum Prozessor zuständig ist. Ladeeinheiten können jeweils bis zu 3 Daten oder Anweisungen gleichzeitig laden, sodass Zen 50 um 2% gestiegen ist, während Speichereinheiten mit 1 Speichersteckplätzen von 2 auf 64 gestiegen sind.

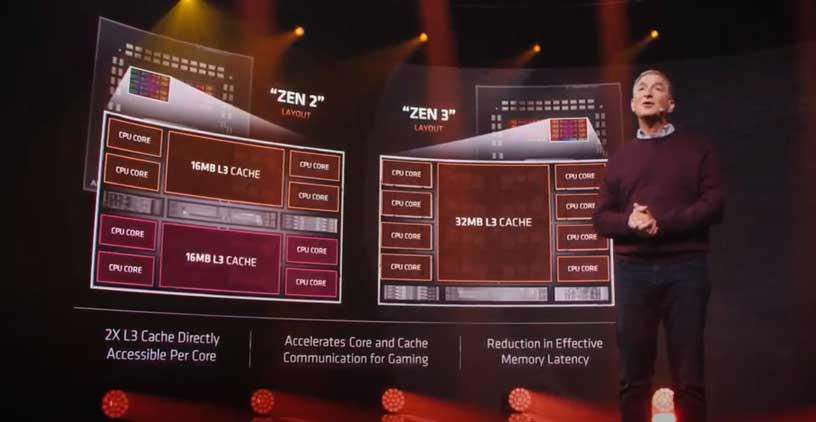

Der neue 8-Core CCX

AMD hat das CCX zum ersten Mal in Zen-Architekturen komplett neu organisiert. Statt 4 Kerne, sondern jetzt 8 Kerne, die Änderungen beinhalten, insbesondere im L3-Cache, der jetzt nicht von 4, sondern von 8 vereinheitlicht und gemeinsam genutzt wird XNUMX Kerne.

Der L3-Cache in Zen-Architekturen ist ein Opfer-Cache. Dies bedeutet, dass er die vom L2-Cache verworfenen Cache-Zeilen übernimmt. Dies bedeutet, dass der L3-Cache nicht an der Anforderung und Erfassung von Daten und Anweisungen aus dem Speicher beteiligt ist. Der Vorteil bei der Verwendung von 8 Kernen besteht also darin, Kerne zu kommunizieren, die sich zuvor in verschiedenen CCXs befanden. Die Kommunikation in diesem Aspekt hat sich verbessert.

Beachten Sie, dass wir mehrere Ausführungsthreads finden können, die miteinander interagieren. Wenn die Kommunikationsentfernung zwischen den verschiedenen Kernen, die denselben Befehl ausführen, zunimmt, erhöht sich auch die Ausführungszeit. Es spielt keine Rolle, ob ein Kern schneller als der andere ist, da der langsamere den schnelleren verlangsamt. Aus diesem Grund hat AMD die 8 Kerne in einem einzigen CCX vereinheitlicht, um Latenzen aufgrund der Interoperabilität zwischen Kernen zu vermeiden.

Nur wenige Änderungen am Prozessor Northbridge

Im Vergleich zu Zen 2 gibt es nur wenige Änderungen gegenüber Northbridge oder Scalable Data Fabric gemäß AMD-Jargon.

- Beim Ryzen 5000 für Desktop, der auf Chiplets basiert, sind die Änderungen in Bezug auf den IOD des Ryzen 3000 nahezu gleich Null, außer bei der Unterstützung schnellerer DDR4-Speicher als die von Zen 2 unterstützten sowie einer besseren Optimierung in Der Grund. zum Energieverbrauch.

- Dasselbe gilt für monolithische SoCs, die auf Zen 3 basieren, mit Ausnahme des neuen CCX. Der Rest des Prozessors ist der gleiche wie bei Zen 2.

Eigentlich sollten wir mit dem Eintreffen von DDR5-Speicher und neuen E / A-Standards wie PCIe 5.0 ein neues SDF oder IOD sehen, aber dies sollte zur gleichen Zeit eintreffen, zu der AMD die Zen 4-Architektur startet, oder wir befinden uns möglicherweise mit einem Ryzen 6000-Serie mit einem neuen IOD, aber mit Zen 3-Kernen, aber das kann nur AMD sagen.