หากคุณติดตามโลกของไมโครโปรเซสเซอร์มาระยะหนึ่งแล้ว สิ่งที่แน่นอนที่สุดคือคุณจะคุ้นเคยกับคำย่อ RISC และ CISC ซึ่งไม่ใช่อะไรมากไปกว่าคำจำกัดความของโครงสร้างของชุดคำสั่งที่โปรเซสเซอร์จัดการ ในช่วงไม่กี่ปีที่ผ่านมากระบวนทัศน์ใหม่ได้รับการขนานนามว่า VISC ประกอบด้วยอะไรบ้าง?

โปรเซสเซอร์ส่วนใหญ่ในตลาดเริ่มน่าเบื่อ เนื่องจากมีการใช้งานเพียงเล็กน้อย อยู่บนพื้นฐานของการปรับปรุงประสิทธิภาพโดยการปรับชิ้นส่วนเล็กๆ ให้ทั้งหมดทำงานได้ดีขึ้นกว่าเดิม แต่ในช่วงไม่กี่ปีที่ผ่านมายังไม่มีการปฏิวัติเหมือนที่เกิดขึ้นกับการดำเนินการที่ไม่เป็นระเบียบในช่วงกลางทศวรรษที่ 90 อย่างไรก็ตามสิ่งนี้สามารถเปลี่ยนแปลงได้ ขอบคุณสถาปัตยกรรม VISC ซึ่งแสดงถึงกระบวนทัศน์ใหม่

VISC เป็นชุดคำสั่งหรือไม่?

สิ่งแรกที่อาจนึกถึงเมื่ออ่านคำย่อเหล่านี้และเนื่องจากความคล้ายคลึงกันคือคำว่า RISC และ CISC ซึ่งอ้างถึงธรรมชาติของชุดการลงทะเบียนและคำแนะนำของโปรเซสเซอร์ซึ่งไม่เกี่ยวกับบทความนี้ตั้งแต่ ภายใต้แนวคิด VISC เราไม่ได้หมายถึงวิธีใหม่ในการจัดหมวดหมู่คำสั่ง แต่หมายถึงสิ่งที่แตกต่างกันโดยสิ้นเชิง

เพื่อให้เข้าใจว่ากระบวนทัศน์ VISC ทำงานอย่างไร เราต้องพิจารณาแนวคิดที่แตกต่างกันสองประการเกี่ยวกับ ซีพียู ประสิทธิภาพ. ประการแรกคือข้อเท็จจริงที่ว่าซีพียูของพีซีในปัจจุบันมีชุดคำสั่งภายในที่เล็กกว่า RISC เนื่องจากสิ่งที่พวกเขาทำคือการถ่ายโอนคำสั่งแต่ละคำสั่งในไมโครอินสตรัคชั่นที่เล็กกว่าภายในระหว่างกระบวนการ ขั้นตอนการถอดรหัส หากเราเป็นคนเจ้าระเบียบ ข้อสรุปในวันนี้ว่าโปรเซสเซอร์ทั้งหมดไม่ใช่ RISC แต่มีชุดคำสั่งที่ลดลงมากซึ่งทำงานภายในและทำหน้าที่สร้างคำสั่งที่เหลือ นั่นคือ ทันทีที่คำสั่งไปถึงหน่วยควบคุม CPU คำสั่งจะถูกแบ่งออกเป็นรายการคำสั่ง

สงครามระหว่าง RISC และ CISC จึงเป็นฝ่ายชนะในสมัยก่อน แต่ด้วยกับดักที่ x86 ซึ่งเป็นสถาปัตยกรรม CISC ที่ใช้กันอย่างแพร่หลายที่สุด ได้สร้างกับดักของพฤติกรรมภายในเหมือน RISC จนถึงทุกวันนี้ ยกเว้น ARM, ISA RISC ส่วนที่เหลือหายไปหรือใกล้จะหายสาบสูญ ยิ่งไปกว่านั้น แม้แต่ ARM ยังได้นำแนวคิดเรื่องการแบ่งคำสั่งออกเป็นคำสั่งที่ง่ายกว่า ดังนั้นกระบวนทัศน์ทั้งสองนอกการกำหนด ISA ทั่วไปของครอบครัวจึงสูญพันธุ์ไปแล้ว

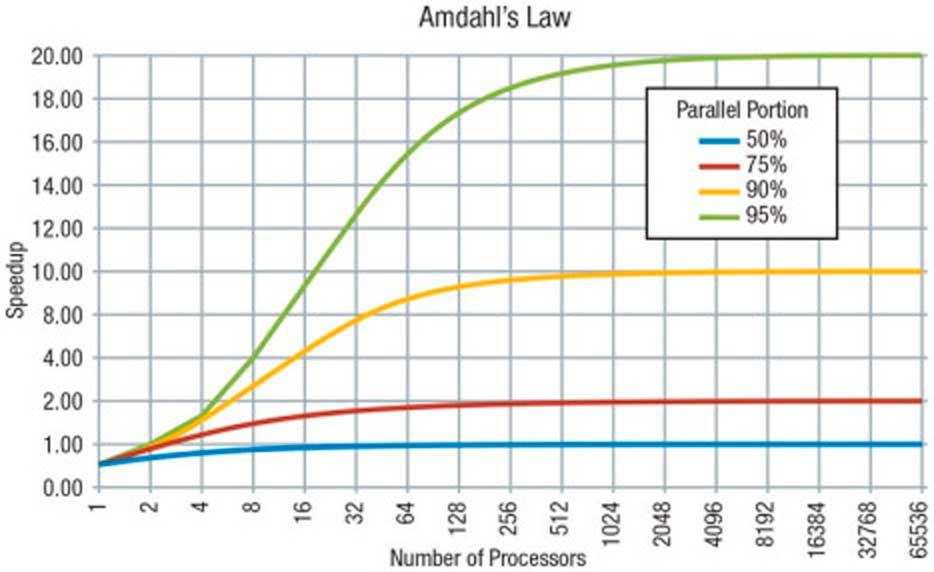

กฎหมายของ Amdahl

เพื่อให้เข้าใจโปรแกรม เราต้องเข้าใจว่าโปรแกรมมีสองส่วนที่แตกต่างกัน:

- หนึ่งที่สามารถดำเนินการในซีรีส์เท่านั้นและสามารถแก้ไขได้โดยเคอร์เนลเดียวเท่านั้นโดยดำเนินการเคอร์เนลการดำเนินการเดี่ยว

- ส่วนนั้นของโค้ดที่รันแบบขนานได้ ซึ่งหมายความว่าสามารถแก้ไขได้โดยหลายคอร์พร้อมกัน และยิ่งมีอยู่ในโปรเซสเซอร์มากเท่าไร ส่วนนี้จะยิ่งได้รับการแก้ไขเร็วขึ้น

หากเราคำนึงถึงสิ่งที่ได้อธิบายไว้ในส่วนก่อนหน้านี้ คุณจะสรุปได้ว่าคำสั่งโปรเซสเซอร์บางตัวที่กลายเป็นไมโครโค้ดที่พวกเขาทำนั้นกลายเป็นชุดคำสั่งที่ต่อเนื่องกันซึ่งสามารถทำงานได้แบบอนุกรมหรือขนานกันระหว่างหลายคอร์ ถึงแม้ว่าปกติจะเป็น คำสั่งส่วนใหญ่จะดำเนินการในเคอร์เนลเดียวและโดยองค์ประกอบที่ใช้ร่วมกันซึ่งโค้ดจะถูกดำเนินการแบบขนาน

ดังนั้นความจริงที่ว่าส่วนหนึ่งของรหัสถูกเรียกใช้งานโดยแกนหลายตัวขึ้นอยู่กับผู้พัฒนาโปรแกรมเท่านั้นซึ่งต้องตั้งโปรแกรมอย่างชัดเจนเพื่อให้บางส่วนทำงานแบบคู่ขนาน

VISC และคอร์เสมือน

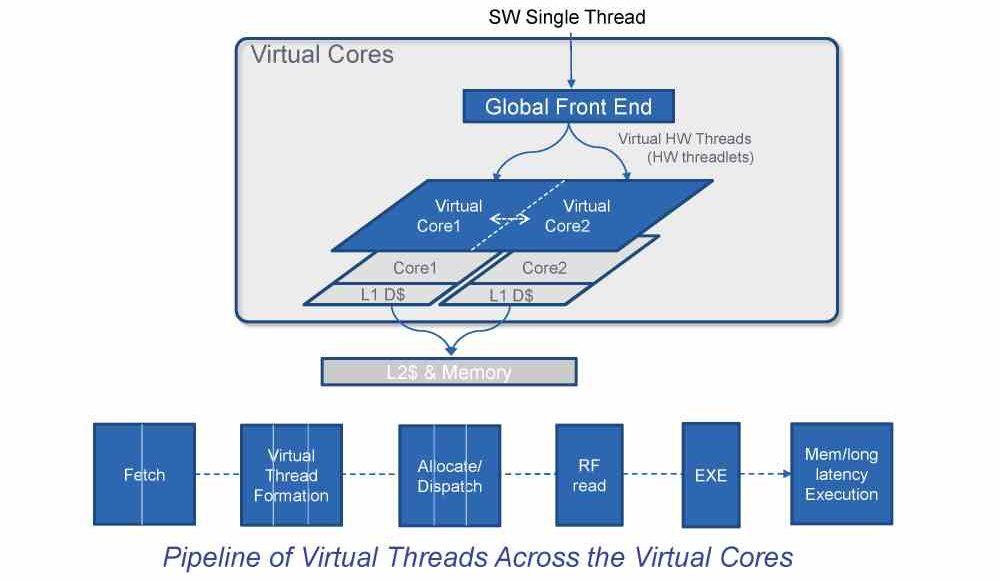

เมื่อเราอธิบายทั้งหมดข้างต้นแล้ว เราสามารถอธิบายความหมายของตัวย่อ VISC ได้ ซึ่งคำจำกัดความคือคำตอบสำหรับคำถามต่อไปนี้: เมื่อสร้าง microinstructions ในขั้นตอนถอดรหัส มันทำงานไม่ได้หรือ ควบคู่ไปกับหลายคอร์แทนที่จะทำในสิ่งเดียวกัน?

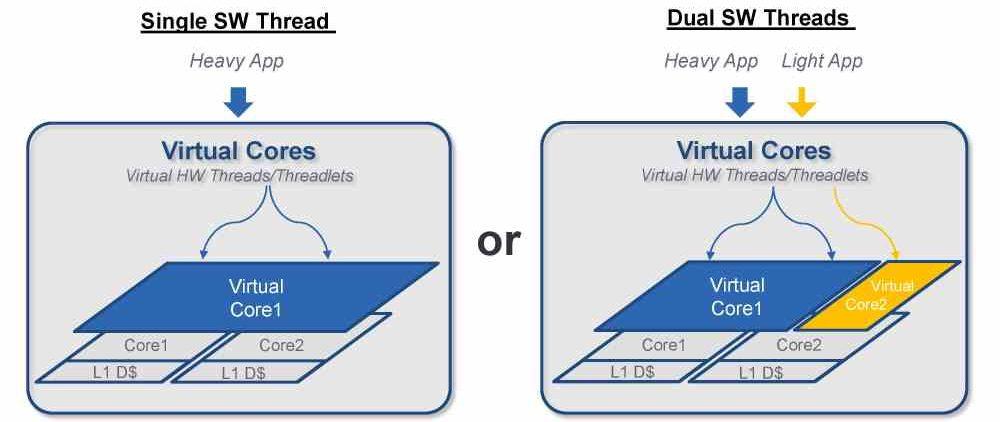

คำตอบสำหรับคำถามเกี่ยวกับสถาปัตยกรรม VISC ซึ่งเปิดตัวครั้งแรกโดยบริษัท Soft Machines ในปี 2015 เพื่อเป็นแนวคิดในการปรับปรุงประสิทธิภาพของ CPU สตาร์ทอัพเล็กๆ นี้ถูกซื้อโดย อินเทล ในปี 2016 และพวกเขาก็ได้ทำงานเพื่อพัฒนาสถาปัตยกรรม VISC นับตั้งแต่นั้นมา มันทำงานอย่างไร? มันสามารถกำหนดได้ง่ายมาก: เธรดเดียวของการดำเนินการถูกส่งไปยัง Global Front End ของโปรเซสเซอร์ ซึ่งจะถูกแปลงเป็นหลาย ๆ อันที่ทำหน้าที่เดียวกันและทำงานแบบขนานและรันในคอร์เสมือน กระบวนการแปลงจะดำเนินการที่ระดับซอฟต์แวร์ผ่านเลเยอร์การแปล แต่เราต้องจำไว้ว่าสิ่งนี้อาจเป็นเรื่องง่ายๆ เหมือนกับไมโครคอนโทรลเลอร์ที่ทำการถ่ายโอนคำสั่ง

ตรงกันข้ามกับสิ่งที่เกิดขึ้นในการกระจายงานในโปรเซสเซอร์แบบมัลติคอร์ทั่วไป ในสถาปัตยกรรม VISC นั้นไม่ได้มีวัตถุประสงค์เพื่อให้คอร์มีอิสระในการดำเนินการตามคำสั่ง แต่องค์ประกอบในการดำเนินการนั้นมีอยู่ในโปรเซสเซอร์เพื่อดำเนินการ ตัวอย่างเช่น อาจเกิดขึ้นได้ว่าในเคอร์เนลทั่วไป ไม่ได้ใช้หน่วยเวกเตอร์ แต่ภายใต้กระบวนทัศน์นี้ สามารถใช้เพื่อสร้างคำสั่งใดคำสั่งหนึ่งได้

VISC และประสิทธิภาพ

เมื่อใช้กระบวนทัศน์ใหม่ในแง่ของสถาปัตยกรรม สิ่งแรกที่ต้องพิจารณาคือผลกระทบต่อประสิทธิภาพการทำงานอย่างไร เนื่องจากไม่คุ้มที่จะเปลี่ยนกระบวนทัศน์ปัจจุบันหากไม่ส่งผลให้ประสิทธิภาพของโปรเซสเซอร์โดยรวมเพิ่มขึ้น วิธีที่คลาสสิกที่สุดในการเพิ่มประสิทธิภาพของโปรเซสเซอร์คือการเพิ่มจำนวนคำสั่งที่แก้ไขได้ต่อรอบสัญญาณนาฬิกา ซึ่งหมายความว่าทำให้ฮาร์ดแวร์มีความซับซ้อนมากขึ้น เนื่องจากการเพิ่มแกนประมวลผล เราต้องนับโครงสร้างพื้นฐานทั้งหมดที่ ล้อมรอบพวกเขาที่กลายเป็นเหมือนหรือซับซ้อนมากขึ้น

สิ่งที่ทำให้ VISC แตกต่างจากที่เหลือคือการกระจายทรัพยากรตัวประมวลผลสำหรับการดำเนินการตามคำสั่งต่างๆ ในรอบสัญญาณนาฬิกาสองสามรอบ ระหว่าง 1 ถึง 4 คอร์ ด้วยวิธีนี้ หากมีคำสั่งสองคำสั่งที่แข่งขันกันเพื่อทรัพยากรอื่นในคอร์ ก็สามารถกำหนดคำสั่งใหม่อย่างรวดเร็วไปยังส่วนอื่นของโปรเซสเซอร์ที่มีทรัพยากรเดียวกันได้

กระบวนทัศน์ปัจจุบัน ซึ่งเป็นการดำเนินการที่ไม่เป็นระเบียบ สิ่งที่ทำคือจัดลำดับการดำเนินการตามคำสั่งใหม่ตามทรัพยากรว่างตลอดเวลา จากนั้นจึงจัดลำดับเอาต์พุตของข้อมูลที่ประมวลผลแล้วใหม่ ข้อจำกัด? การจัดสรรทรัพยากรดำเนินการในระดับแกนเดียวมากกว่าระดับมัลติคอร์ และนี่คือกุญแจสู่ประสิทธิภาพที่สูงขึ้นสำหรับสถาปัตยกรรม VISC

โปรเซสเซอร์เหล่านี้มีอยู่ในปัจจุบันหรือไม่?

แม้ว่าแนวคิดจะดีมากบนกระดาษ แต่ยังไม่มีใครนำเสนอโปรเซสเซอร์ที่ทำงานภายใต้กระบวนทัศน์นี้ แต่เนื่องจากเรากำลังเข้าใกล้ขอบเขตของกระบวนทัศน์ปัจจุบันอย่างค่อยเป็นค่อยไป สิ่งสำคัญคือต้องจำไว้ว่ามีวิธีแก้ไขที่สามารถใช้ได้ เพื่อปรับปรุงประสิทธิภาพ CPU ของพีซีของเราในอนาคต

การมีโปรเซสเซอร์ที่ทรงพลังกว่านั้นไม่เพียงแต่จะมีหนึ่งคอร์ที่เร็วขึ้นหรือมีคอร์มากขึ้นเท่านั้น แต่ยังขึ้นอยู่กับการรู้วิธีใช้ประโยชน์จากทรัพยากรที่มีอยู่ด้วย การดำเนินการที่ไม่เป็นระเบียบเป็นขั้นตอนแรกในแง่นั้น อย่างไรก็ตาม นับตั้งแต่นั้นมานอกเหนือจากการใช้มัลติคอร์ การเปลี่ยนแปลงก็มักจะเกิดขึ้นเพียงเล็กน้อย VISC ยังคงเป็นแนวคิด แต่ก็ไม่ใช่เรื่องที่เป็นไปไม่ได้ และเป็นวิธีใช้ประโยชน์จากทรัพยากรที่มีอยู่ในโปรเซสเซอร์อย่างมีประสิทธิภาพมากขึ้น

จนถึงตอนนี้ เรารู้ว่าแนวคิดนี้เป็นไปได้ใน CPU เนื่องจาก Soft Machines ออกแบบและสร้างขึ้นด้วยกระบวนทัศน์นี้ ดังนั้นถึงแม้จะอยู่ในระดับทดลอง เราก็ทราบดีว่าการออกแบบดังกล่าวสามารถทำได้ อีกสิ่งที่แตกต่างกันคือความยากลำบากในการนำชุดคำสั่ง x86 ทั้งชุดและลงทะเบียนไปยังกระบวนทัศน์นี้ ซึ่งมีความซับซ้อนอย่างยิ่งโดยธรรมชาติ