ในอีกไม่กี่ปีข้างหน้า โหนด N5 ของโรงหล่อที่ใหญ่ที่สุดในเอเชียจะกลายเป็นโหนดการผลิตที่สำคัญที่สุดในอีกไม่กี่ปีข้างหน้า จากการวิเคราะห์หนึ่งในชิปที่ผลิตขึ้นแล้วภายใต้กระบวนการผลิตดังกล่าว พบว่า ความหนาแน่นของโหนด 5nm ของ TSMC ต่ำกว่าที่คาดไว้ . นี่เป็นข่าวร้ายหรือขาดความจริงใจจากคุณหรือเปล่า?

โหนด 5nm ของ TSMC และรุ่นต่างๆ จะกลายเป็นส่วนที่เกี่ยวข้องมากที่สุดในอีกไม่กี่ปีข้างหน้าภายในพีซี ไม่เพียงเพราะความจริงที่ว่า เอเอ็มดี จะใช้สำหรับชิปในอนาคตเช่น Ryzen 7000, EPYC Genoa และ GPU RX 7000 เราลืมไม่ได้ว่า TSMC ยังเป็นลูกค้าและแม้กระทั่ง อินเทลเนื่องจากกราฟิกแบบรวมใน Meteor Lake และส่วนประกอบกราฟิก Ponte Vecchio HPC บางตัวจะใช้สำหรับการผลิต ดังนั้น ไม่ทางใดก็ทางหนึ่ง ผู้เล่นหลักในอุตสาหกรรมใช้ประโยชน์จากโหนดการผลิตนี้ไม่ทางใดก็ทางหนึ่ง แม้ว่าในขณะนี้ ชิปเดียวที่ใช้กระบวนการผลิตนี้คือชิปของ Apple

ความหนาแน่นของโหนด 5nm ของ TSMC ต่ำกว่าที่โฆษณาไว้

แม้ว่าพาดหัวข่าวนี้อาจดูเหมือนเป็นลบ แต่ก็มีคำอธิบายและจาก Angstronomics พวกเขาได้สร้างบทความที่น่าสนใจที่พวกเขาแจ้งให้เราทราบถึงสาเหตุที่ TSMC กำหนดความหนาแน่นของโหนด 5nm ผิด เราหมายถึงจำนวนทรานซิสเตอร์ต่อพื้นที่และความซับซ้อนของชิปที่สามารถสร้างได้ โรงหล่อไต้หวันระบุอย่างเป็นทางการว่าเป็น 171 ล้านทรานซิสเตอร์ต่อตารางมิลลิเมตร . อย่างไรก็ตาม จากการวิเคราะห์อย่างละเอียดพบว่า ตัวเลขนี้ต่ำกว่าและเป็น 137.6 ล้านทรานซิสเตอร์ต่อตารางมิลลิเมตร .

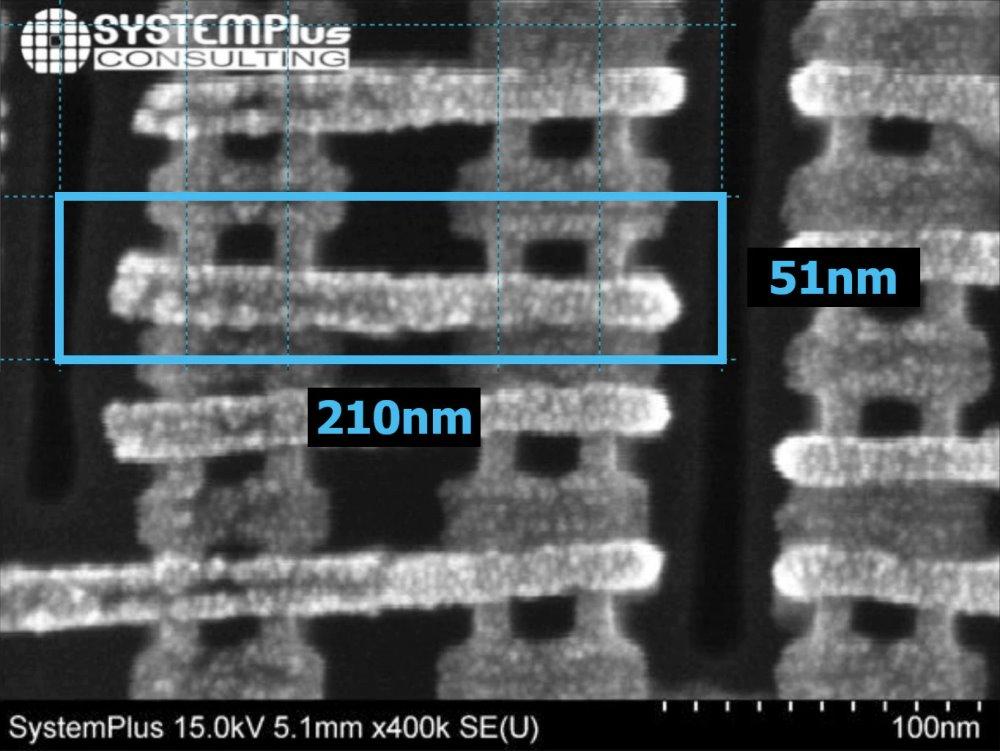

พวกเขาทำสิ่งนี้โดยการวัดผ่านกล้องจุลทรรศน์อิเล็กทรอนิกส์ขนาดของทรานซิสเตอร์ที่ใช้ในการสร้างโปรเซสเซอร์ Apple A15 รุ่นล่าสุด iPhone. ซึ่งวัด 210 nm ใน Cell Height และ 51 nm ใน CPP . ค่าทั้งสองถูกนำมาใช้ในการเปรียบเทียบเพื่อทราบขนาดของทรานซิสเตอร์เมื่อเทียบกับโหนดก่อนหน้า ดังนั้นโหนด N7 ของ TSMC จึงมีค่าของ 240nm และ 57nm ตามลำดับ ให้ความหนาแน่นของ 90.64 ล้านทรานซิสเตอร์ต่อตารางมิลลิเมตร . ในกรณีของโหนด 10 มม. ของ Intel ซึ่งเพิ่งตั้งชื่อ Intel 7 เมื่อไม่นานมานี้ เรากำลังพูดถึงตัวเลขของ 100.33.

ถ้าตัวเลขทำให้คุณเวียนหัวก็ไม่ต้องกังวล ซึ่งหมายความว่านักออกแบบสามารถใส่ชิปพื้นที่เดียวกันได้ถึง ประตูลอจิกเพิ่มขึ้น 51.8% บนชิปที่สร้างขึ้น 5nm มากกว่าชิป 7nm . ซึ่งหมายความว่าไม่ใช่การกระโดดแบบเต็มโหนด อันที่จริงทรานซิสเตอร์นั้นไม่ใช่ 5 นาโนเมตรด้วยซ้ำ เนื่องจากเมตริกนี้ไม่สอดคล้องกับความเป็นจริงไปนานแล้วและเป็นเครื่องมือทางการตลาดมากกว่า

TSMC ให้ตัวเลขเท็จหรือไม่?

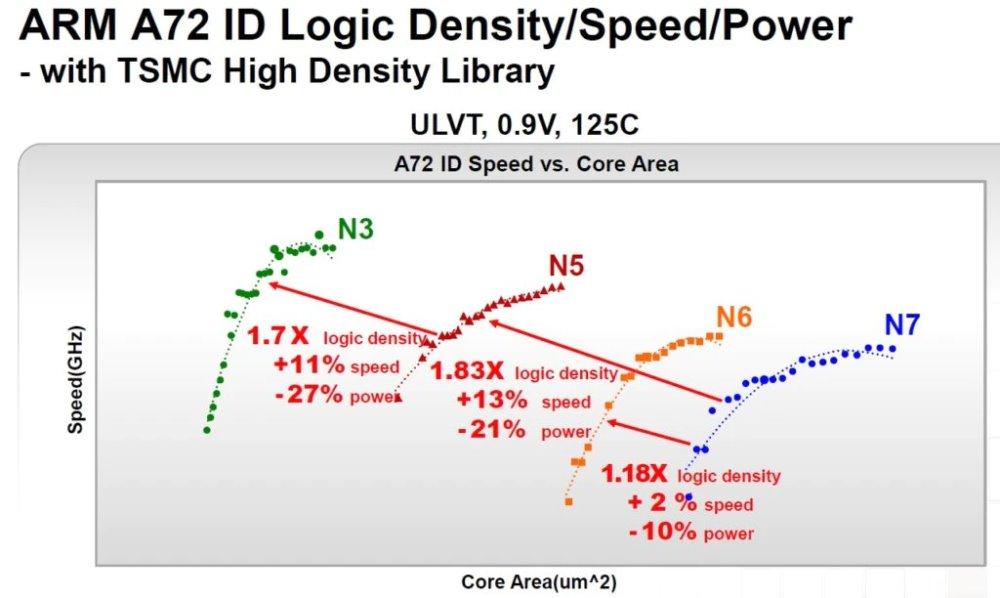

ไม่ ไม่ได้จริงๆ และนี่เป็นเพราะโรงหล่อชาวไต้หวันไม่ได้ใช้ตัวชี้วัดที่เราได้กล่าวถึงในส่วนก่อนหน้านี้ สิ่งที่ TSMC มักทำคือปรับชิปที่รู้จักแล้วให้เข้ากับโหนดใหม่เพื่อรับเมตริก สำหรับสิ่งนี้พวกเขาใช้การออกแบบของ Cortex A72 แน่นอนเนื่องจากเป็นการออกแบบที่ไร้เหตุผล โรงหล่อจึงมีอิสระทั้งหมดในโลกเมื่อพูดถึงการใช้ทรานซิสเตอร์ประเภทใดประเภทหนึ่งเพื่อสร้างตรรกะที่แตกต่างกัน ประตูที่ประกอบขึ้นเป็นชิป

ดังที่คุณเห็นในภาพด้านบนเส้นเหล่านี้ เราสามารถสรุปได้ว่า TSMC ได้ตัวเลขมาจากที่ใด . และมันคือว่ามันหมายถึงความหนาแน่นของตรรกะเท่านั้น ตัวอย่างเช่น SRAM หรือชิ้นส่วนแอนะล็อกของชิปถูกตัดออก อย่างไรก็ตาม จะเห็นได้ว่าการกระโดดจากโหนดปัจจุบันไปยังโหนดในอนาคตนั้นไม่ส่งผลให้ประหยัดการบริโภคได้มากหรือเพิ่มความเร็วได้อย่างมีนัยสำคัญ ซึ่งส่วนหนึ่งอธิบายการบริโภคที่เพิ่มขึ้นของรุ่นไฮเอนด์ของกราฟิกการ์ดรุ่นต่อไปจาก NVIDIA และเอเอ็มดี

ไม่ว่าในกรณีใดสิ่งนี้จะไม่ส่งผลกระทบต่อพันธมิตรของโรงหล่อและชิปในอนาคตที่จะทำในนั้น หลายคนทำเสร็จแล้วและกำลังจะพิมพ์ลงบนแผ่นเวเฟอร์ในขนาดใหญ่