There are certain myths or legends regarding CPUs that in many occasions do not correspond to reality, while in others they can be quite similar. One of these myths is the well-known relationship between the density of transistors versus the performance of a CPU and above all, against the IPC. What is truth and how much lie in this?

There are users who for different reasons maintain this almost cognitive association when talking about performance per core. This is extrapolated more simply on a topic as hot as the nanometer comparison between Intel and AMD, or even within the companies themselves.

In the end, the average user focuses precisely on nanometers as if they were an actual measurement measure that impacts CPU performance. Let’s see and reason if this is true.

Nanometers vs. Transistor Density vs. Performance

The lithography of a processor is directly related to the number of transistors that each chip is capable of accommodating, but as we all know, there are a number of relationships added to this entire process.

A greater number of transistors requires in certain types of wafers and lithographic processes a remodeling or even a new type of transistor. We are currently experiencing it with the move to EUV and it will be so in the future with other jumps.

The paradigm shift with transistors and their evolutions inevitably marks a change in the instructions per cycle that they are capable of working, opening or closing according to the architecture of the same. But although everything said so far is true, the performance of a CPU as such, speaking and generalizing the concept, is not only due to it.

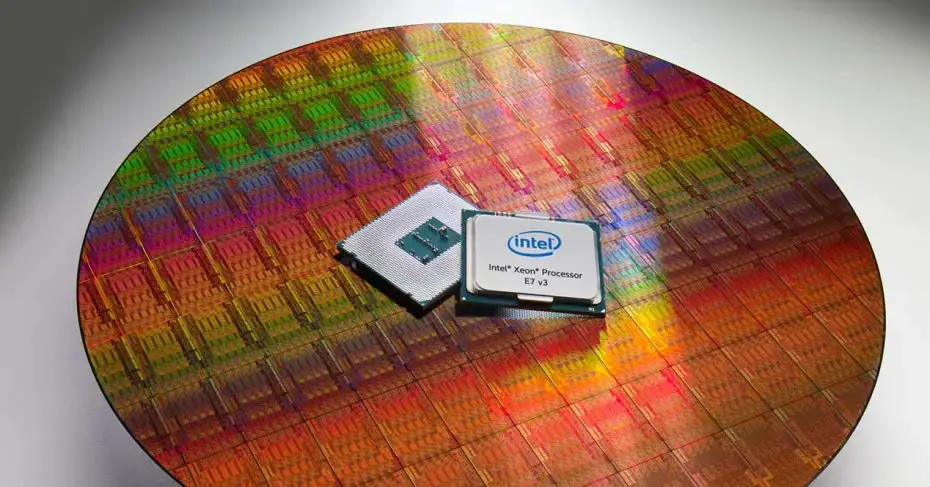

The best test has been offered by Intel, where its 14 nm with a density much lower than AMD’s 7 nm achieve very similar results in terms of performance. In addition and continuing with the example above, within its 14 nm we find from the Broadwell-E architecture to Comet Lake-H and finally Rocket Lake-S at the end of the year.

Are they directly dependent? what influences?

Therefore, and although there is an inescapable relationship, the density of transistors is not directly proportional to performance and does not influence it as such. Including a greater number of transistors per square centimeter supposes a very high technological advance and in many occasions several problems that lead to worse overclocking, worse series frequencies or higher consumption.

Continuing with the general and higher level concept, we cannot affirm that the relationship between the two is directly dependent. The biggest performance jump is mainly due to improvements in the CPU architecture, which together with a higher frequency than usually provided by the most advanced lithographic processes can cause them to trigger.

But logically this does not mean that a higher performance (not IPC) is obtained by density, but because the lithographic process is able to offer more in less space, with less consumption and at higher speeds, but above all, higher performance is obtained by improvements in architecture.

You have to separate the terms well, because it is easy to fall into the density vs. performance trap when very large improvements in architecture coincide with a reduction in the lithographic process. Something similar to what happened in Zen 2 with AMD: passing at 7 nm ( 95 MTr / mm2 ) important structural changes in architecture, higher frequencies and equal consumption.