Almost a year ago, Intel unveiled one of the most relevant technologies for this decade and with it an architecture that surprised everyone by the approach and implementation that the blues are going to carry out. This architecture is LakeField , which has been in development for decades and that we will have the privilege to contemplate, but what is it and why is it so revolutionary?

The approach that Intel has taken to this architecture and SoC may seem complicated, but the reality is that just as ARM has entered to compete more or less decently in the server and desktop market, now Intel is going to try assault the market for smartphones, televisions and in general the so-called IoT .

LakeField is not a step, but a leap into the future because of what it represents and how it is designed, which at the same time is the most interesting thing about architecture.

Intel LakeField, 3D implementation reaches the chips of the future

Let’s put the main cards on the entrance table to understand the type of technology we are referring to and that listing them, will be easier to understand:

- We are facing a mobile SoC.

- Ultra low consumption ( 2 mW ).

- Intel’s first real multi-core architecture.

- First Penta Core in its history.

- The company’s first chip based on the big.LITTLE concept.

- Integrated Gen 11 iGPU .

- Foveros technology with 3D chip packaging.

- Support for LPDDR4X .

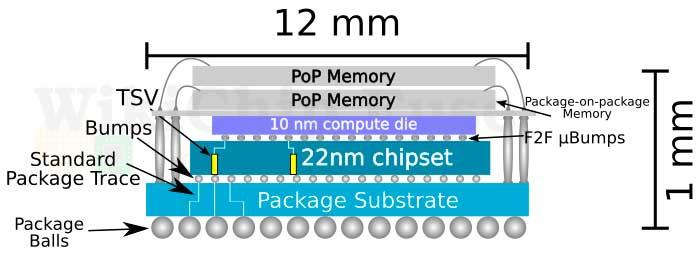

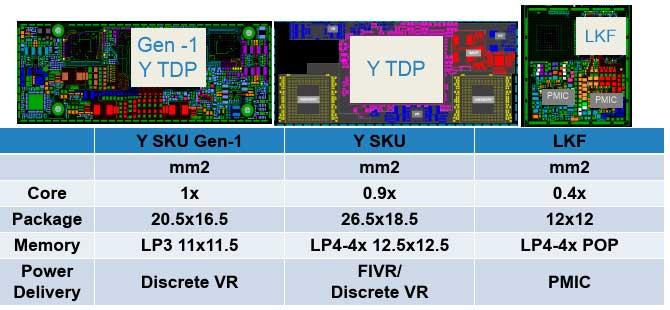

- It will only occupy 12 x 12 mm with 1 mm height.

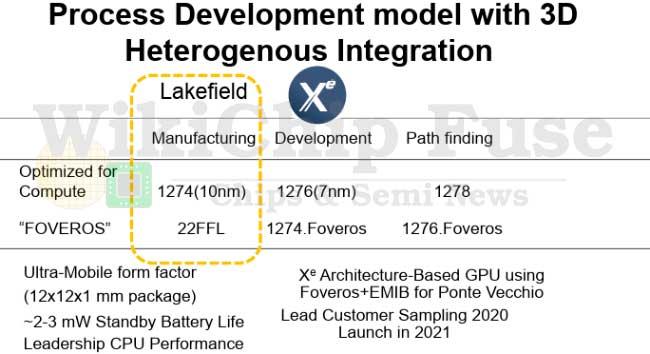

Many concepts, a lot of innovation and above all many years of development that will lay the pillar of the new generation processors, not only from Intel, but from AMD and the rest of companies that want to be able to compete. The entire sector is focused on the so-called 3D package, let’s not kid ourselves, it is the future and soon it will be the present, but to understand it it is necessary to understand how LakeField is made.

3D stacking, the foundation of the new generation of dies

It is not difficult to understand the concept of 3D dies. They are chips that are vertically linked, one on top of the other with different technologies that we already talked about, such as EMIB, Foveros or Co-EMIB through ODI.

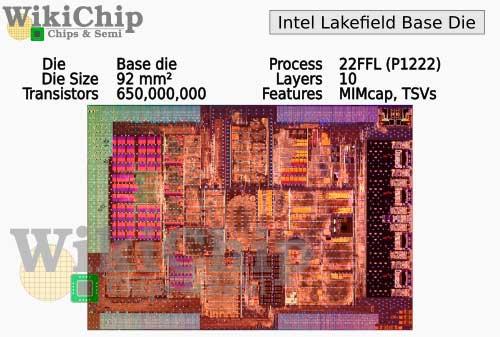

At LakeField Intel has been equally ambitious and smart, the substrate (matrix) has been used for all the functions that Intel calls “low power”. This includes the USB-C 3.0 interface, some lower performance input and output buses and especially the PCIe Gen 3 interface.

As a good base, it will be greater than the final size of the chip and boasts 92 mm2 under the 22 nm FFL process, also called 22FFL, which although it may not seem like it by its nomenclature, is really a very specific process for this type of products that are It is based on 14nm, but it is optimized for mobile SoCs.

Therefore the transistors will be recorded at 14nm and thereby facilitate the efficiency of the entire matrix. It’s cheap, it has enhanced capabilities specific to this type of product, and it has fewer layers than a normal die, so it has the best of Intel saving its new 10nm and next 7nm, where the cost is still very high.

The die is the most advanced created to date by Intel

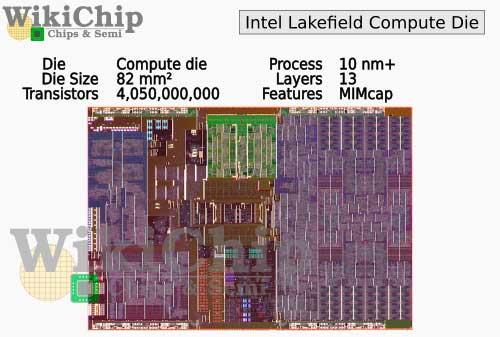

Given its base, we are going to introduce ourselves with the die itself, where all the benefits and novelties of this architecture and chip are. We are talking about a die of only 82 mm2 with more than 4 billion transistors, which shows that the density is absolutely brutal and not seen until now.

This has its explanation, and it is that LakeField will arrive under the new 10 nm + from Intel, that is, the second generation of its new lithographic process that increases the frequency considerably compared to its second version and improves the final density a little. Here it must be emphasized that, it seems, 37% of the chip will be spent on the iGPU, which shows the effort that Intel has to make with Gen 12 to make integrated graphics cards more powerful and with less final area in a die.

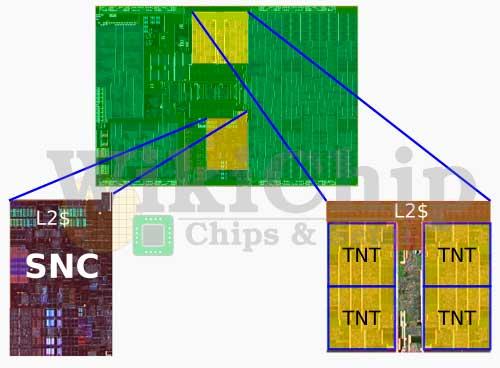

As for the cores themselves, we will find four based on the Tremont architecture and a single Sunny Cove, where Intel has not enabled Hyper Threading. This has been done in this way to facilitate the distribution of tasks in the operating systems, since it seems that this technology will take time for developers to perform as expected.

The advantage here on the other hand is that a Tremont core at the same frequency as a Sunny Cove will achieve up to 70% of its performance, but with an infinitely lower consumption.

This requires workloads to arrive in bursts for the largest of cores, while background processes are managed by the 4 Tremont cores, thus saving a lot of energy.

Lastly, all four Tremont cores are estimated to be similar in size to the Sunny Cove core, including their caches and AVX-512 instructions (deactivated as standard), so we can get an idea of the potential that future chips could have. almost to same area.

Foveros

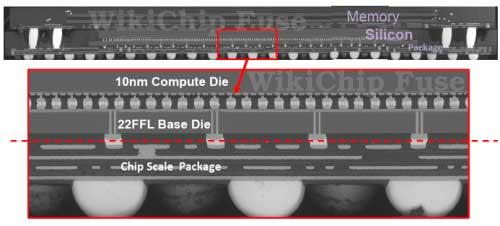

We have already talked long and hard about this technology and its sisters, so we will skip the theoretical part to briefly comment on how Intel plans to arrange its chips vertically. We will have two main layers plus the LPDDR4X RAM memory chips, which is impressive.

The matrix is linked “face to face” with the 22nm LFF substrate using 50um micro bumps and this in turn with the main package. Memories are deposited just above the cores and their 10nm + matrix with 350 micron TSVs for interconnection. Therefore and summing up, we have 5 layers in total on a chip that measures 12mm2 and 1mm in height.

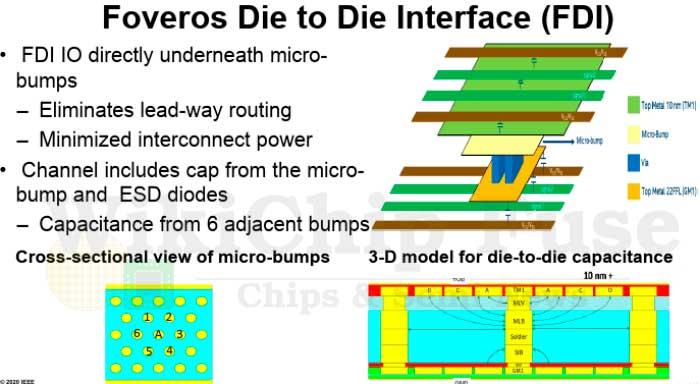

The communication interfaces are made using what Intel has called the FDI or Foveros Die Interface, where the maximum speed they reach between matrices is 500 MT / s and per lane. Considering that it has more than 200 lanes with the same clock, we have a really amazing bandwidth for a chip of that size.

To finish this section, it should be borne in mind that this provision of diets ends with a different form factor that includes a power supply through the TSVs, which has been called PMIC and has nothing to do with the mobile U and Y series voltage controllers.

LakeField, the future of 3D stacking

As we have already seen with Co-EMIB and ODI , the future of the company lies in improving what exists with LakeField. The first step will be to improve efficiency and costs, to gradually implement various improvements that require new CAD creation systems, power supplies, ESD, signal integrity and a long etc …

What Intel will look for in a short period of time is to combine low-power cores with very high-performance cores, including Xe GPUs with HBM and all in the same vertical 3D package that offers the best of all worlds.