In many processors, especially those of some generations ago from Intel, we could see the abbreviation IMC engraved on the IHS. Currently they no longer do, but that does not mean that they have stopped using it and, in fact, today it is one of the components of the processors that has more importance . In relation to this, do you know what the BMI of a processor is? In this article we tell you, and we explain how it works and the types there are.

The IMC is really one of those parts of the processor that are not usually taken into account, and that is that we only tend to look at the cores, the speed, and at most the cache memory they have. But it is an internal component of the processors that is extremely important, and then you will discover why.

What is the BMI of a processor

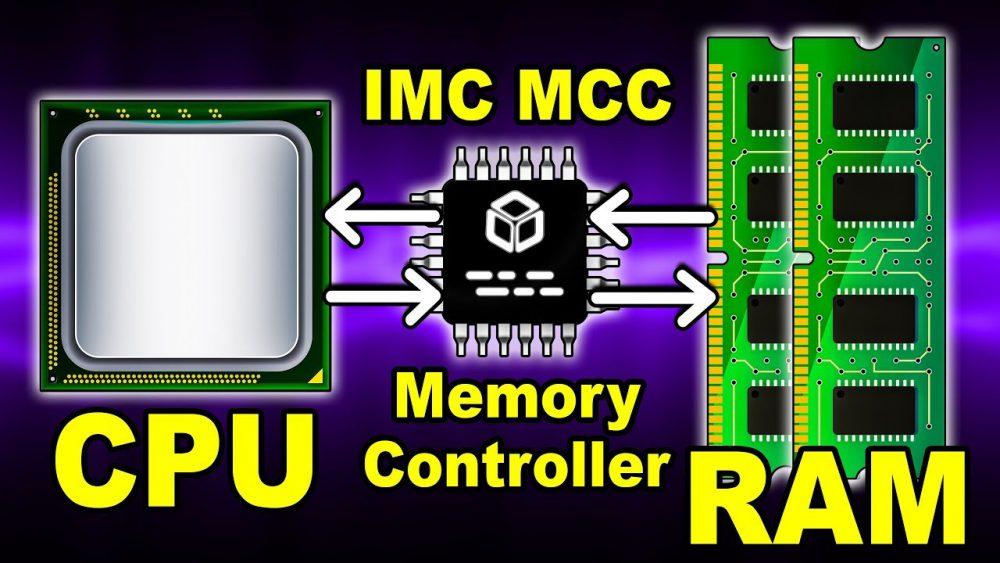

IMC stands for “Integrated Memory Controller”, or Integrated Memory Controller. The memory controller can be separated or integrated in another chip, so those that are integrated are those that, as you will suppose, are integrated in the die of the processor. Formerly the memory controller was on the motherboard, but for quite some time now only IMC have been used, since it allows the processor to control the memory in a faster and more direct way.

The IMC is therefore the digital circuit that controls the flow of data that comes and goes between the processor itself and the RAM. That it is integrated in the processor allows RAM management to be performed more directly and quickly than when the memory controllers were on the motherboard.

Before the AMD K8s (released in 2003), AMD processors had the memory controller in their northbridge, but in the following generations AMD pioneered integrating it into the processor itself . Intel first did the same for Nehalem processors, in 2008, and thereafter both manufacturers use only IMC. Incidentally, ARM architecture processors also use, in all cases, a memory controller built into the processor.

How does the memory controller work?

Memory controllers contain the logic necessary to read and write to RAM, and to “refresh” the DRAM. Without these constant “refreshments”, the DRAM would lose the data it contains since the capacitors they contain lose their charge in a fraction of a second (no more than 64 milliseconds per the JEDEC specification ).

Reading and writing to RAM is done by selecting the DRAM row and column data addresses as the inputs to the multiplexer circuit, where the demultiplexer in the DRAM uses the converted inputs to select the correct memory location and return the data, which are returned back through a multiplexer to consolidate in order to reduce the bus width required for operation.

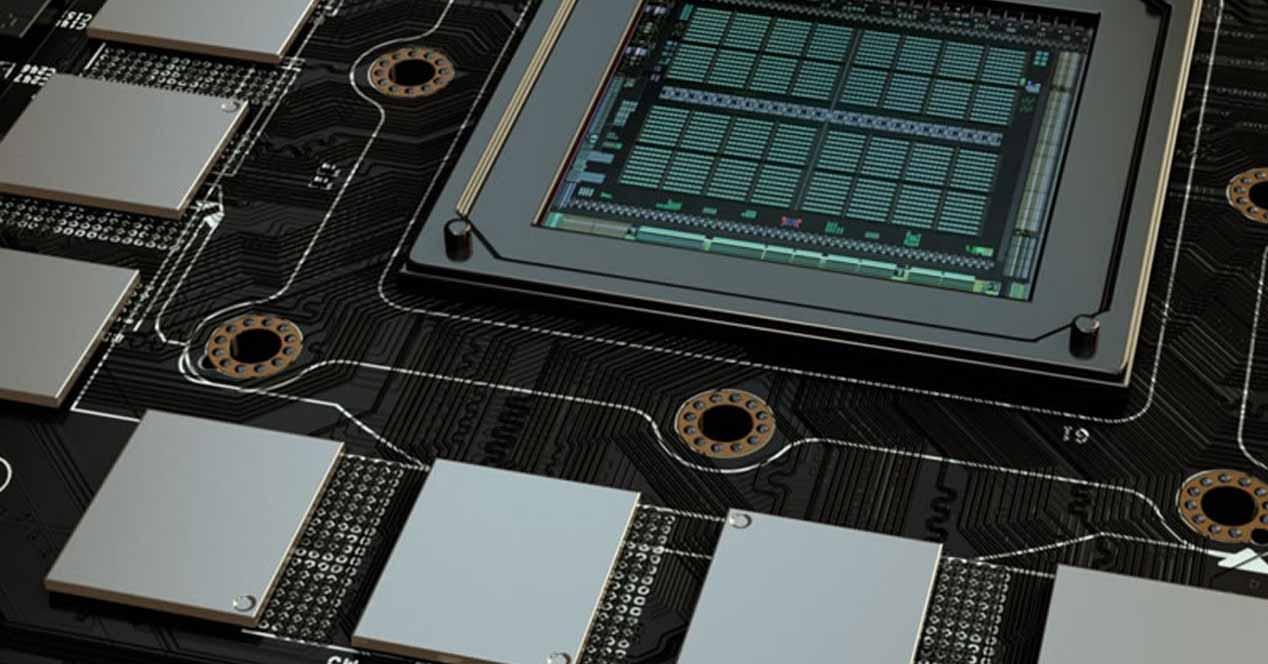

The memory bus width represents the number of parallel lines available to communicate with the memory cell. The bus width of memory controllers varies from 8 bits on older systems to 512 bits on more modern video cards and systems (typically implemented as four simultaneous 64-bit memory controllers that operate in parallel, although some are designed to operate in “group mode” where two 64-bit memory controllers can be used to access a 128-bit memory device).

Some memory controllers also have their own error correction system that can be complemented with the one that incorporates many RAM memory modules in itself (which is good because it frees them up in some cases, and doubles the size error correction in others).

Variants of existing BMI

Surely you have noticed that the specifications of the processors almost always include a definition of the type and speed of RAM with which they are compatible, precisely depending on the BMI they incorporate. Therefore, there are different variants of memory controller, and some of them you will surely recognize immediately.

On the one hand there are DDR controllers that can be (commonly) dual-channel and quad-channel . The difference is that in these the RAM memory is separated into 2 or 4 separate channels, each with a direct bus to the memory controller. These are the most used on PCs, and the ones we all know.

On the other hand we have the controllers called FBM ( Fully Buffered Memory ) whose behavior differs from the previous one in that a buffer device is placed in each memory module (called FB-DIMM ) that uses a serial data link to the controller (instead if parallel), decreasing the number of rails needed to communicate at the expense of increasing latency.

Finally, we have Flash memory controllers, used by devices such as pen drives or SSDs. Flash memory is inherently slower than DRAM and generally becomes unusable after a number of write cycles, but it still needs to have its own memory controller to communicate with the rest of the system.