VLIW est l'abréviation de Very Long Instruction Word, qui se traduit par des instructions de mots très longs. Dans le monde de l'architecture des processeurs, il est utilisé pour définir un type de Processeur ou processeur qui réalise le parallélisme d'instructions ou ILP, mais avec une méthodologie différente de celle utilisée dans les processeurs superscalaires, qui est celle couramment utilisée dans les CPU.

Les processeurs de type VLIW présentent un certain nombre d'avantages et d'inconvénients par rapport aux autres processeurs et ont non seulement été utilisés dans les processeurs, mais aussi comme unités de shader pour les GPU et également dans les DSP.

Aujourd'hui, les conceptions VLIW semblent avoir disparu du matériel PC, mais elles restent une option valable dans la conception de nouveaux processeurs pour différents domaines du marché du matériel malgré leur désuétude.

Comment fonctionne un processeur VLIW?

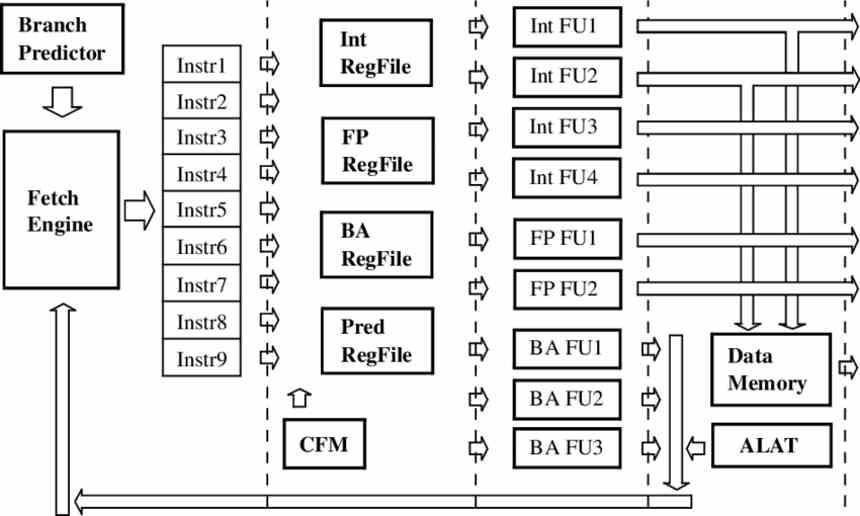

Dans un processeur superscalaire ou ILP conventionnel, les instructions sont capturées et traitées individuellement pendant le cycle d'instructions de chacune. Qu'il s'agisse d'une exécution dans l'ordre ou dans le désordre. Dans le cas d'un processeur VLIW, il s'agit de regrouper plusieurs instructions en une seule et de les envoyer ensemble aux différentes unités disponibles dans le processeur.

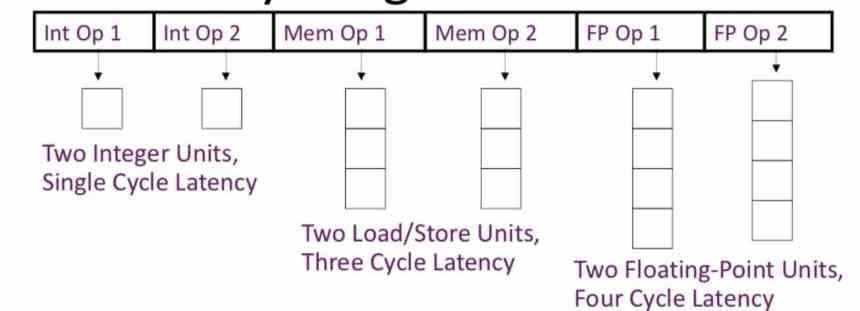

Pour y parvenir, les processeurs VLIW dépendent fortement du compilateur lors de la génération du code binaire , qui regroupera les différentes instructions en une seule instruction, en tenant toujours compte du niveau d'occupation de chacune des unités d'exécution à chaque instant de fonctionnement. l'exécution, qui dépendra du nombre de cycles d'horloge requis par chacune des instructions.

Étant donné que les instructions peuvent avoir différents degrés de durée en termes de cycles d'horloge, c'est un problème de performance, car pendant plusieurs cycles d'horloge, nous aurons des unités d'exécution qui ne feront rien et qui exécuteront une instruction NOP, ce qui signifie que pendant cette horloge cycle, ladite unité n'effectue aucune opération. Cela rend les processeurs VLIW fortement dépendants du compilateur pour une efficacité maximale.

Avantages et inconvénients d'une conception VLIW

Les avantages qu'il apporte sont principalement les suivants:

- Le matériel en charge du décodage des instructions est beaucoup plus simple qu'un CPU ILP ou TLP, cela permet de laisser plus d'espace libre sur la puce pour les unités d'exécution et donc de pouvoir exécuter plus d'instructions en même temps.

- Avoir plus d'espace vous permet également de placer un plus grand nombre de registres, ce qui est idéal pour faciliter l'exécution spéculative typique des processeurs dans le désordre sans avoir besoin d'un tampon de tri.

En ce qui concerne ses inconvénients, le premier d'entre eux est dans le fait qu'un compilateur beaucoup plus complexe est nécessaire, le second étant celui que nous avons mentionné précédemment et qui repose sur le fait qu'il y a un plus grand gaspillage des différentes unités d'exécution, puisque la plupart d'entre eux vont passer un bon moment inoccupé.

Pour mieux le comprendre, imaginez que vous ayez regroupé dans un VLIW 3 instructions qui nécessitent les 4 premiers cycles pour être exécutés, le deuxième 7 cycles et le troisième 10 cycles. L'unité d'exécution chargée d'exécuter la première instruction aura 6 cycles d'horloge sans rien faire, la seconde 3 et tout cela car la troisième aura besoin de 10 cycles pour fonctionner.

D'autre part, il faut ajouter le fait que bien qu'au niveau des instructions les binaires ne changent pas, lors du développement d'un nouveau CPU, il est possible qu'une instruction existe déjà augmente ou diminue le nombre de cycles. Cela rend un compilateur différent nécessaire même pour les nouvelles itérations d'un nouveau processeur, ce qui rend difficile le lancement de versions plus avancées d'un processeur et nécessite dans de nombreux cas la création d'un compilateur binaire en binaire, qui réorganise les instructions pour le nouveau processeur.

Génération d'instructions par le compilateur

Pour que vous puissiez mieux le comprendre, nous avons préparé quelques listes, la première est l'exécution dans un processeur superscalaire ou connu sous le nom d'ILP, la seconde est un processeur de type VLIW.

À partir d'un processeur de type ILP, une liste de ses instructions serait la suivante:

- Charger A1

- Charge B1

- Charger A2

- Facturer B2

- Multipliez les valeurs de A1 et B1

- Ajouter les valeurs de A2 et B2

- Ajouter A1 et A2

- Cargaison A3

- Charge B3

- Multiplier A3 par B3

- Ajoutez B1 et B2.

D'un autre côté, un processeur VLIW regroupera plusieurs des instructions en une seule:

- L'A2 et le B2 sont chargés simultanément

- Chargez A2 et B2, multipliez A1 et B1, ajoutez A2 et B2.

- Chargez A3, B3, multipliez A3 par B3 et ajoutez B1 et B2.

Le fait que nous ayons réussi à regrouper les 11 instructions en seulement 3 très grandes instructions signifie que le temps nécessaire à chacune des instructions VLIW sera au plus le temps nécessaire pour l'instruction la plus complexe du groupe d'instructions.

Accès mémoire de ce type de processeurs

Comme nous l'avons vu précédemment, les processeurs VLIW dépendent du compilateur et ajoutent souvent des instructions NOP au code lors de la compilation. La raison de cela est que la création d'un CPU VLIW avec des instructions de taille variable est extrêmement complexe, donc cela est fait est de créer une taille fixe de bits à laquelle le CPU lit les instructions et récupère cette quantité de données de la mémoire à chaque cycle. . et instructions.

Cela signifie que les processeurs VLIW nécessitent des bus de données beaucoup plus larges que les processeurs conventionnels en raison du fait qu'ils regroupent un grand nombre de bits à chaque fois qu'ils capturent de nouvelles instructions à exécuter. Ceci étant son grand talon d'Achille, car dans les processeurs ILP, courants dans les processeurs PC, des largeurs de données plus étroites et donc des contrôleurs de mémoire plus simples sont utilisés.

La chose normale dans les processeurs VLIW est qu'ils capturent les instructions suivantes à exécuter pendant que l'instruction VLIW actuelle est en cours d'exécution. Car en regroupant plusieurs instructions en une seule, le temps de capture de chacune d'elles séparément est réduit.