Dans une conférence qui Intel a donné en Chine, le président du centre de recherche que l'entreprise a dans ce pays a parlé des objectifs qu'ils ont pour 2030 et qui peuvent se résumer à rendre les puces HP de plus en plus petites et qui consomment à chaque fois moins. Ce qui se traduit par un plus grand nombre de transistors et une plus grande efficacité énergétique . Comment comptent-ils y parvenir ?

La loi de Moore, qui a été inventée par le fondateur d'Intel et qui ne peut pas non plus être considérée comme une loi, mais plutôt comme une observation, est souvent mal interprétée car les concepts à son sujet sont souvent confus. Dans tous les cas, il faut préciser qu'il ne s'agit pas de l'économie des puces ou de leur puissance, mais de la densité de transistors dans un espace donné qui double de temps en temps. Bien que cela ait ralenti au fil du temps, la réalité est qu'il est toujours valable aujourd'hui.

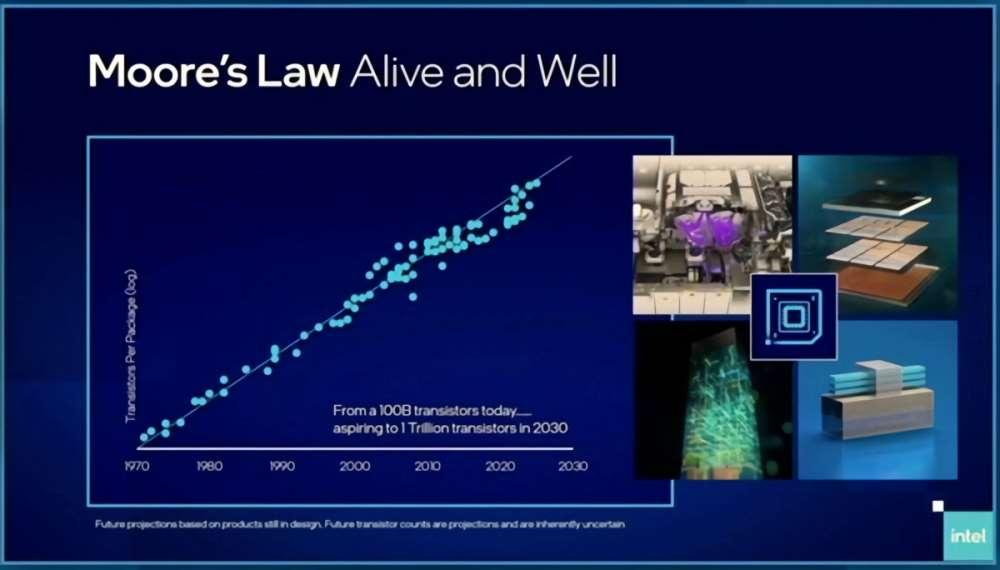

Un billion de puces à transistors d'ici 2030 d'Intel

Pour ceux d'entre nous qui suivent l'évolution du monde des puces, c'est-à-dire des semi-conducteurs, il nous apparaît très clairement aujourd'hui que l'avenir, pour pouvoir doubler de temps en temps la densité des transistors, passe par l'utilisation de nouvelles techniques de fabrication. et la conception, en particulier des concepts tels que les puces éclatées, et l'utilisation de structures tridimensionnelles, c'est-à-dire l'empilement de puces les unes sur les autres et tout cela pour fabriquer des puces qui sera jusqu'à 10 fois plus efficace et qui abritera jusqu'à un billion de dollars à l'intérieur. de transistors.

Actuellement, la puce la plus complexe utilisée dans les PC est NVIDIA's AD102, que nous pensons être le central GPU du RTX 4090, qui a une densité de 7.6% par rapport à cet objectif, nous parlons donc d'un temps assez long pour qu'Intel atteigne cet objectif, de plus, ils ont envisagé d'y arriver d'ici 2030, bien que nous ne le fassions pas savoir s'ils le feront dans leurs processeurs Core ou, à l'inverse, dans leurs GPU ARC. N'oublions pas que les microprocesseurs dits désintégrés, ou chiplets, permettent de casser la limite de treillis du wafer et de créer des compositions avec un plus grand nombre de transistors que dans une puce monolithique.

Dans tous les cas, il faut garder à l'esprit qu'une fois les puces monobloc expédiées, le panorama aura complètement changé, car cela signifiera l'utilisation évidente de puces plus petites, qui est également poursuivie en raison de l'augmentation des coûts que chaque nouveau nœud de fabrication de puces.

Un ordre de grandeur d'amélioration de l'efficacité énergétique

Si nous parlons déjà d'efficacité énergétique, ce que nous devons prendre en compte, c'est que ces mots, bien qu'il s'agisse d'un objectif louable pour des choses comme la réduction de l'empreinte carbone. Nous ne pouvons pas oublier que nous ne connaissons pas la puissance avec laquelle ils veulent mesurer ce paramètre et le type de matériel, ainsi que les tests de performances qu'ils envisagent d'utiliser comme référence ou à défaut aujourd'hui, des paramètres tels que la maison d'instructions par seconde, puissance en virgule flottante, etc.

C'est un objectif qui ne sera pas facile à atteindre et qui nécessitera la mise en place de plusieurs technologies, dont plusieurs sont encore en développement et d'autres bientôt déployées. Nous parlons de choses comme les transistors de type RibbonFET pour des densités de 2 nanomètres ou moins, les alimentations Power VIA, l'utilisation de systèmes de lithographie avancés qui sont actuellement inconnus et de nouveaux systèmes de conditionnement de puces similaires à Foveros.