Wenn Sie die Welt der Mikroprozessoren schon länger verfolgen, werden Sie sicherlich mit den Akronymen RISC und CISC vertraut sein, die nichts anderes sind als eine Definition der Struktur des Befehlssatzes, den ein Prozessor verarbeitet. Nun, in den letzten Jahren ist ein neues Paradigma aufgetaucht, das VISC genannt wird. Woraus besteht es?

Die meisten Prozessoren auf dem Markt sind langweilig geworden, da sie wenig auf den Tisch bringen. Sie basieren darauf, die Leistung zu verbessern, indem kleine Teile so angepasst werden, dass das Ganze besser funktioniert als zuvor, aber in den letzten Jahren gab es keine Revolution wie die, die Mitte der 90er Jahre mit der Ausführung außerhalb der Ordnung stattfand, aber dies könnte sich ändern dank VISC-Architekturen, die ein neues Paradigma darstellen.

Ist VISC eine Anleitung?

Das erste, was einem beim Lesen dieser Akronyme in den Sinn kommt, sind aufgrund ihrer Ähnlichkeit die Wörter RISC und CISC, die sich auf die Art der Register und Anweisungen des Prozessors beziehen, die nicht Gegenstand dieses Artikels sind, da unter dem VISC-Konzept beziehen wir uns nicht auf eine neue Art der Kategorisierung von Anweisungen, sondern auf etwas ganz anderes.

Um zu verstehen, wie das VISC-Paradigma funktioniert, müssen wir zwei verschiedene Konzepte in Bezug auf CPU Leistung. Die erste davon ist die Tatsache, dass PC-CPUs heute einen internen Befehlssatz haben, der sogar noch kleiner ist als RISC, da sie während des Prozesses jede der Befehle intern in kleineren Mikrobefehlen übertragen. Entschlüsselungsphase. Wenn wir Puristen sind, ist die Schlussfolgerung, dass heute alle Prozessoren nicht RISC sind, sondern dass sie einen sehr reduzierten Satz von Anweisungen haben, der intern arbeitet und dazu dient, den Rest der Anweisungen zu erstellen. Das heißt, sobald ein Befehl die CPU-Steuereinheit erreicht, wird er in eine Liste von Befehlen zerlegt.

Der Krieg zwischen RISC und CISC wurde also von ersterem gewonnen, aber mit der Falle, dass x86, die am weitesten verbreitete CISC-Architektur, die Falle machte, sich intern wie ein RISC zu verhalten. Bis heute, außer ARM, der Rest der ISA RISC fehlt oder steht kurz vor dem Verschwinden. Darüber hinaus hat sogar ARM das Konzept übernommen, die Anweisungen in einfachere zu unterteilen, sodass beide Paradigmen außerhalb der Definition des gemeinsamen ISA einer Familie bereits ausgestorben sind.

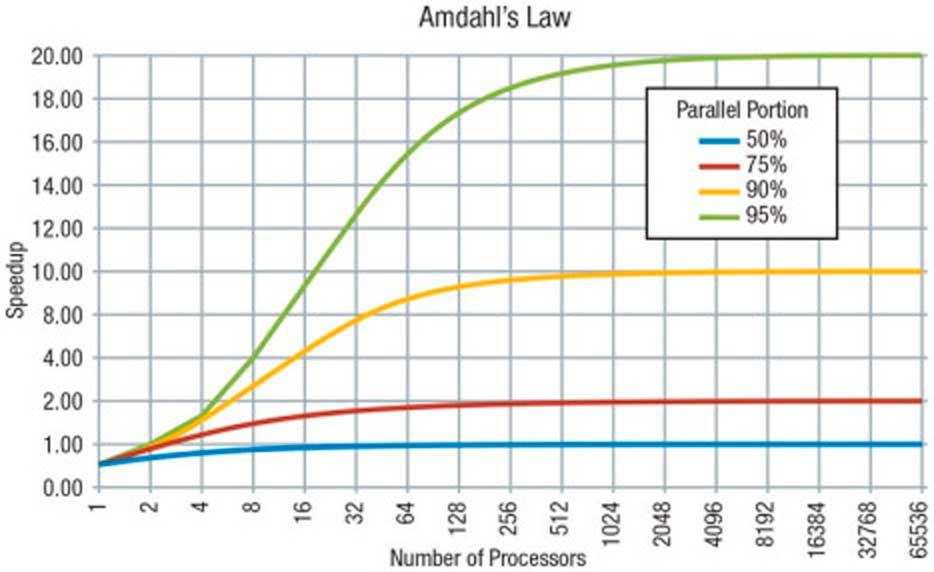

Amdahls Gesetz

Um ein Programm zu verstehen, müssen wir verstehen, dass ein Programm aus zwei verschiedenen Teilen besteht:

- Diejenige, die nur seriell ausgeführt werden kann und daher nur von einem einzelnen Kernel durch Ausführen eines Solo-Ausführungskernels gelöst werden kann.

- Der Teil des Codes, der parallel ausgeführt werden kann, also von mehreren Kernen gleichzeitig gelöst werden kann und je mehr davon im Prozessor sind, desto schneller wird dieser Teil gelöst.

Wenn wir berücksichtigen, was im vorherigen Abschnitt erklärt wurde, werden Sie zu dem Schluss kommen, dass einige der Prozessorbefehle, die zu Mikrocode werden, eine Folge von Befehlen sind, die seriell oder parallel zwischen mehreren Kernen arbeiten können, obwohl dies üblich ist dass die meisten Anweisungen in einem einzigen Kernel ausgeführt werden und dass der Code durch gemeinsame Elemente parallel ausgeführt wird.

Dass ein Teil des Codes von mehreren Kernen ausgeführt wird, hängt daher ausschließlich vom Programmentwickler ab, der ihn explizit programmieren muss, damit bestimmte Teile parallel arbeiten.

VISC und virtuelle Kerne

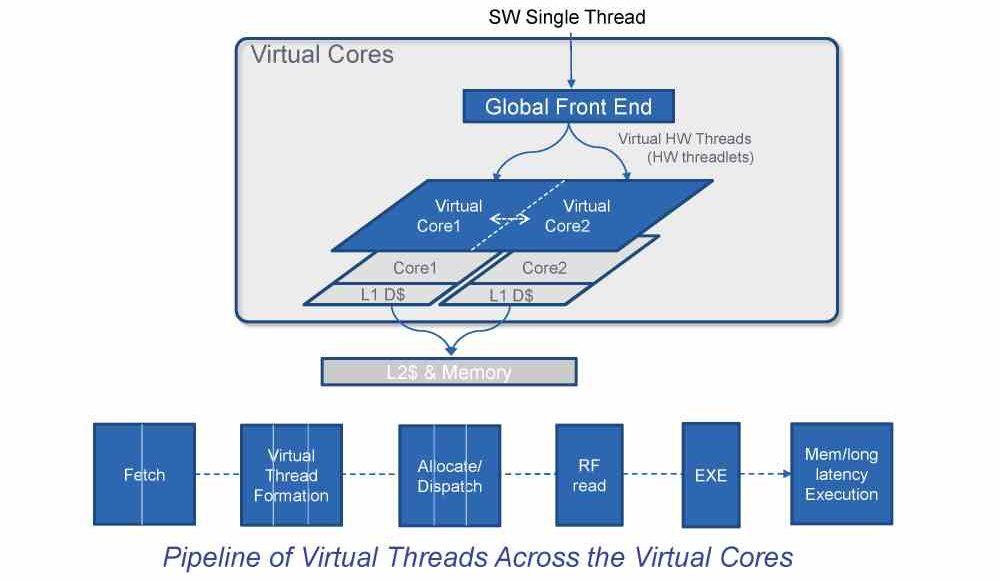

Nachdem wir all das oben erklärt haben, können wir erklären, was das Akronym VISC bedeutet, dessen Definition die direkte Antwort auf die folgende Frage ist: Wenn die Mikrobefehle in der Dekodierungsphase generiert werden, können sie nicht funktionieren? parallel mit mehreren Kernen statt in einem einzigen dito?

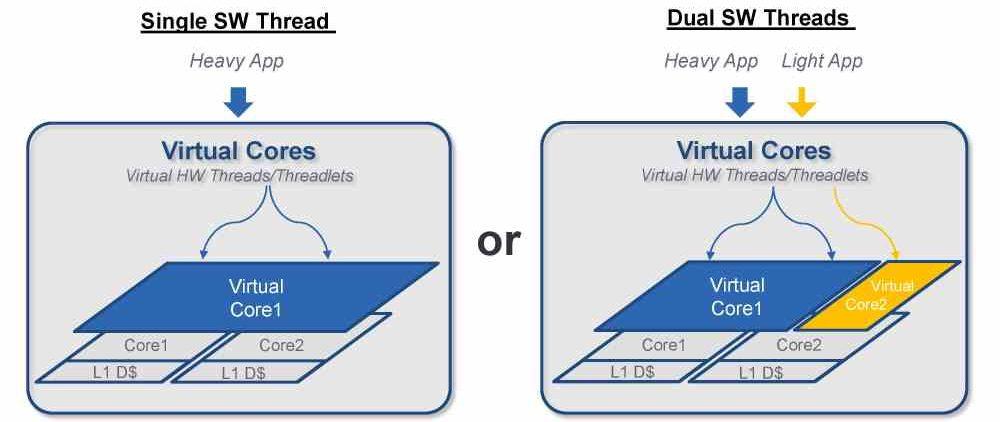

Nun, die Antwort auf die Frage nach der VISC-Architektur, die erstmals 2015 von einer Firma namens Soft Machines als Konzept zur Verbesserung der CPU-Leistung gestellt wurde. Dieses kleine Startup wurde gekauft von Intel im Jahr 2016 und arbeiten seitdem an der Entwicklung einer VISC-Architektur. Wie funktioniert es? Nun, es lässt sich sehr einfach definieren: Ein einzelner Ausführungsthread wird an das Global Front End des Prozessors gesendet, der in mehrere umgewandelt wird, die dieselbe Funktion ausführen und parallel arbeiten und in virtuellen Kernen laufen. Der Konvertierungsprozess wird auf Softwareebene durch eine Übersetzungsschicht ausgeführt, aber wir müssen bedenken, dass dies so einfach sein kann wie ein Mikrocontroller, der die Übertragung der Anweisungen durchführt.

Anders als bei der Aufgabenverteilung in einem herkömmlichen Multicore-Prozessor ist bei einer VISC-Architektur nicht beabsichtigt, dass ein Kern frei ist, um einen Befehl auszuführen, sondern dass die Elemente, um ihn auszuführen, innerhalb des Prozessors verfügbar sind, um ihn auszuführen. Zum Beispiel kann es vorkommen, dass in einem herkömmlichen Kernel die Vektoreinheit nicht verwendet wird, aber unter diesem Paradigma kann sie verwendet werden, um eine der Anweisungen zu bilden.

VISC und Leistung

Bei der Übernahme eines neuen Paradigmas in Bezug auf die Architektur ist zunächst zu berücksichtigen, wie sich dieses auf die Leistung auswirkt, da es sich nicht lohnt, das aktuelle Paradigma zu ändern, wenn dies nicht zu einer Erhöhung der Gesamtprozessorleistung führt. Der klassischste Weg, die Leistung eines Prozessors zu erhöhen, besteht darin, die Anzahl der Befehle zu erhöhen, die pro Taktzyklus gelöst werden. Dies bedeutet, dass die Hardware immer komplexer wird, da wir beim Hinzufügen der Kerne die gesamte Infrastruktur zählen müssen, die sie umgibt, die gleich oder komplexer werden.

Was VISC vom Rest unterscheidet, ist nichts anderes, als dass die Verteilung der Prozessorressourcen für die Ausführung der verschiedenen Befehle in wenigen Taktzyklen zwischen 1 und 4 Kernen erfolgt. Wenn zwei Befehle in einem Kern um andere Ressourcen konkurrieren, können sie auf diese Weise sehr schnell einem anderen Teil des Prozessors zugewiesen werden, in dem dieselben Ressourcen verfügbar sind.

Das aktuelle Paradigma, die Ausführung außerhalb der Reihenfolge, besteht darin, die Ausführung der Anweisungen jederzeit gemäß den freien Ressourcen neu zu ordnen und dann die Ausgabe bereits verarbeiteter Daten neu zu ordnen. Die Einschränkung? Die Ressourcenzuweisung erfolgt auf Single-Core- und nicht auf Multi-Core-Ebene, und dies ist der Schlüssel zu höherer Leistung für VISC-Architekturen.

Gibt es diese Prozessoren heute?

Obwohl das Konzept auf dem Papier sehr gut ist, hat noch niemand einen Prozessor vorgestellt, der nach diesem Paradigma funktioniert, aber da wir uns allmählich an die Grenzen des aktuellen Paradigmas stoßen, ist es wichtig zu bedenken, dass es Lösungen gibt, die dienen können um die CPU-Leistung unserer PCs für die Zukunft zu verbessern.

Ein leistungsfähigerer Prozessor bedeutet nicht nur einen schnelleren oder mehr Kerne, sondern basiert auch auf dem Wissen, wie man die verfügbaren Ressourcen optimal nutzt. Die Ausführung außerhalb der Reihenfolge war der erste Schritt in diesem Sinne, aber seitdem sind die Änderungen außerhalb der Umstellung auf Multicore im Allgemeinen geringfügig. VISC ist immer noch ein Konzept, aber es ist kein unmögliches und es ist eine Möglichkeit, die im Prozessor verfügbaren Ressourcen viel effizienter zu nutzen.

Bisher wissen wir, dass das Konzept in einer CPU möglich ist, da Soft Machines eine mit diesem Paradigma entwickelt und gebaut hat. Obwohl es sich um eine experimentelle Ebene handelte, wissen wir, dass ein solches Design möglich ist. Ein anderer Unterschied ist die Schwierigkeit, den gesamten Satz von x86-Befehlen und -Registern in dieses Paradigma zu bringen, das von Natur aus äußerst komplex ist.